文書番号: ESC-APN-022-02

# H2X600/HLX600

ターゲット・インターフェース仕様

## はじめに

「H2X600/HLX600 ターゲット I/F 仕様」(以下、本書)は、H2X600/HLX600 とユーザーシステムを接続するためのターゲット I/F 仕様および注意事項を示したドキュメントです。

特にユーザーシステム側にご注意いただきたい事項は、以下の通りです。

- ユーザーインターフェース仕様(コネクタ仕様、信号のピンアサイン仕様、プルアップ/プルダウン仕様)

- 高速信号に関する基板パターン設計注意事項

- その他、注意事項

H2X600 と HLX600 に共通的な内容の説明において、 H2X600 と HLX600 を総称して、"ICE"と表記しています。

# 本書の対象となるユーザー

H2X600/HLX600 をお使いになる、すべてのユーザー。

## 注意事項

- 本書の内容は、H2X600 を基準にして解説しています。そのため、HLX600 をご使用の場合には、一部の 名称や参照しているマニュアル名が異なる場合があります。

- advice シリーズの製品を安全にお使いいただくために重要な情報は、以下に示すマニュアルに記載されています。

- adviceLUNA II: 『adviceLUNA II ユーザーズマニュアル(固有編)』(H2X600\_podm\_jpn.pdf)

- adviceLUNA: 『adviceLUNAユーザーズマニュアル(固有編)』(HLX600\_podm\_jpn.pdf)

- 本ガイドに記載されている会社名・製品名は、各社の登録商標または商標です。

## アイコンについて

本ガイドで使用しているアイコンには、以下の意味があります。

特に重要な情報を記載しています。操作する際は十分に注意してください。

操作を進める上で役に立つ情報やアドバイスなどの補足事項を記載しています。

本ガイドのほかのページやほかのマニュアルなどの参照情報を記載しています。

# 内容

| はじめに                                          | 1    |

|-----------------------------------------------|------|

| 本書の対象となるユーザー                                  | 1    |

| 注意事項                                          | 2    |

| アイコンについて                                      | 2    |

| 1. 接続可能なターゲット・インターフェース                        | 4    |

| 1.1. 概要                                       |      |

| 2. 詳細仕様                                       | 5    |

| 2.1. 20 ピン JTAG インターフェース(AE741/AE737)         | 5    |

| 2.1.1. 適合コネクタ                                 | 5    |

| 2.1.2. コネクタのピン配置図                             | 5    |

| 2.1.3. コネクタのピンアサイン                            | 6    |

| 2.1.4. ユーザーシステムに必要な回路                         | 8    |

| 2.2. 38 ピン ETM インターフェース(H2X600XP/HLX600TP)    | . 12 |

| 2.2.1. 適合コネクタ                                 | . 12 |

| 2.2.2. コネクタのピン配置図                             | . 12 |

| 2.2.3. コネクタのピンアサイン                            | . 13 |

| 2.2.4. ユーザーシステムに必要な回路                         | . 17 |

| 2.3. 14 ピン JTAG インターフェース(AE221)               | . 22 |

| 2.3.1. 適合コネクタ                                 | . 22 |

| 2.3.2. コネクタのピン配置図                             | . 22 |

| 2.3.3. コネクタのピンアサイン                            | . 23 |

| 2.3.4. ユーザーシステムに必要な回路                         | . 24 |

| 2.4. 20-14 ピン Xtensa 純正 ICE 準拠インターフェース(AE729) | . 25 |

| 2.4.1. 適合コネクタ                                 | . 25 |

| 2.4.2. コネクタのピン配置図                             | . 25 |

| 2.4.3. コネクタのピンアサイン                            | . 26 |

| 2.4.4. ユーザーシステムに必要な回路                         | . 27 |

| 2.5. ユーザーシステム結線の注意事項                          | . 28 |

| 3. 補足事項                                       | . 32 |

| 3.1. 適合コネクタについて                               | . 32 |

| 3.2. ユーザーシステムに必要な回路について                       | . 32 |

| 4. 参考資料                                       |      |

| 改訂履歴                                          |      |

## 1. 接続可能なターゲット・インターフェース

## 1.1. 概要

接続可能なターゲット・インターフェースとそれに対応したプローブの製品型名を以下に示します。

| No. | プローブ製品型名      | コネクタ           | 接続可能なインターフェース                                |

|-----|---------------|----------------|----------------------------------------------|

|     |               | (ケーブル型名)       |                                              |

| 1   | adviceLUNA II | • MICTOR 38pin | ETM/JTAG/SWD インターフェース                        |

|     | • H2X600XP    |                | 1) ハードマクロコア(ARM7TDMI,ARM9TDMI など)*2          |

|     |               |                | 2) ソフトマクロコア (ARM7TDMI-S,ARM9E-S,ARM11 など) *2 |

|     | adviceLUNA    |                | 3) CoreSight ETM/CoreSight JTAG インターフェース     |

|     | · HLX600TP    |                | 4) CoreSight ETM/CoreSight SWD インターフェース      |

| 2   | adviceLUNA II | · DIL 20pin    | JTAG/SWD インターフェース                            |

|     | • H2X600JP    | (AE741/AE737)  | 1) ハードマクロコア(ARM7TDMI,ARM9TDMI など)*2          |

|     |               |                | 2) ソフトマクロコア (ARM7TDMI-S,ARM9E-S,ARM11 など) *2 |

|     | adviceLUNA    |                | 3) CoreSight JTAG インターフェース                   |

|     | · HLX600JP    |                | 4) CoreSight SWD インターフェース                    |

|     |               | • DIL 14pin    | JTAG インターフェース                                |

|     | *1            | (AE221)        | 1) ハードマクロコア(ARM7TDMI,ARM9TDMI など)*2          |

|     |               | · DIL 14pin    | JTAG インターフェース                                |

|     |               | (AE729)        | 1) Xtensa 純正 ICE 準拠インターフェース                  |

- \*1 H2X600JP/HLX600JP をご使用の場合は、ETM 機能(トレース機能)は使用できません。

- \*2 ARM7/ARM9/ARM11 には、ソフトマクロコアとハードマクロコアが存在します。 ソフトマクロコア(ARM7TDMI-S,ARM9E-S など)に接続する場合には、14 ピン JTAG インターフェースでは接続 できません。

<識別方法>

ソフトマクロコア: MPU 名称に"-S"がついている場合(ARM7TDMI-S,ARM9E-S など)

または、MPUに RTCK 端子がある場合

ハードマクロコア: MPU 名称に"-S"がついていない場合(ARM7TDMI,ARM9TDMI など)

または、MPUに RTCK 端子がない場合

プローブを誤挿入すると、機器の破損、焼損に至る場合があります。 ユーザーシステム側のコネクタは、プローブの誤挿入を防止するため、必ず指定の誤挿入防止ガイドキー付きのコネクタを実装してください。

プローブの誤挿入による機器の損傷は、有償修理扱いとなります。

# 2. 詳細仕様

# 2.1. 20 ピン JTAG インターフェース(AE741/AE737)

## 2.1.1. 適合コネクタ

| インターフェース | メーカー  | 適合コネクタ                                                              | 仕様                                 |

|----------|-------|---------------------------------------------------------------------|------------------------------------|

| 20ピンJTAG | ヒロセ電機 | ライトアングル                                                             | 2.54mm ピッチピンヘッダ                    |

| インターフェース |       | <ul><li>HIF3FC-20PA-2.54DS</li><li>HIF3FC-20PA-2.54DS(71)</li></ul> | DIP タイプ 20 ピン<br>(Embedded-ICE 準拠) |

|          |       | ストレート<br>・HIF3FRC-20PA-2.54DSA<br>・HIF3FRC-20PA-2.54DSA(71)         |                                    |

## 2.1.2. コネクタのピン配置図

コネクタ実装面視

#### 2.1.3. コネクタのピンアサイン

### ① CoreSight/ARM7/ARM9/ARM11 JTAG インターフェースの場合

| ピン | I/O | Signal name | ピン | I/O | Signal name |    |

|----|-----|-------------|----|-----|-------------|----|

| 20 | -   | GND         | 19 | OUT | DBGACK      | *1 |

| 18 | -   | GND         | 17 | IN  | DBGRQ       | *1 |

| 16 | -   | GND         | 15 | O/D | nSRST       | *2 |

| 14 | -   | GND         | 13 | OUT | TDO         |    |

| 12 | -   | GND         | 11 | OUT | RTCK        | *4 |

| 10 | -   | GND         | 9  | IN  | TCK         |    |

| 8  | -   | GND         | 7  | IN  | TMS         |    |

| 6  | -   | GND *5      | 5  | IN  | TDI         |    |

| 4  | -   | GND.        | 3  | O/D | nTRST       | *2 |

| 2  | -   | VSupply *3  | 1  | -   | VTref       | *3 |

I/O 方向は、ユーザーシステム側(MPU)から見た入出力方向を示します。

● IN : ICE → ユーザーシステム

●OUT : ユーザーシステム  $\rightarrow$  ICE  $\rightarrow$  INOUT : ユーザーシステム  $\leftrightarrow$  ICE

●O/Dは、オープンドレインです。双方向信号となります。

- \*1 ご使用の MPU によってはアサインされていない場合があります。 『ユーザーシステムに必要な回路』『ユーザーシステム結線の注意事項』をご覧になり、指示に従い端子処 理してください。

- \*2 オープンドレイン端子です。ユーザーシステム上の信号と WIRED-OR してください。

- \*3 ユーザーシステムの JTAG 信号の I/O 電源に接続してください。詳細は『ユーザーシステム結線の注意事項』 をご覧ください。

- \*4 TCKのループバック信号です。『ユーザーシステムに必要な回路』『ユーザーシステム結線の注意事項』をご覧になり、指示に従い端子処理してください。

- \*5 ユーザーシステムの GND に必ず接続してください。

- 6番 pin は、ICE のプローブが接続されていることを検知するために使用します。そのため、ユーザーシステム側で GND に接続しておく必要があります。

### ② CoreSight SWD インターフェースの場合

| ピン | I/O | Signal name |    | ピン | I/O   | Signal name |    |

|----|-----|-------------|----|----|-------|-------------|----|

| 20 | -   | GND         |    | 19 | OUT   | DBGACK      | *1 |

| 18 | -   | GND         |    | 17 | IN    | DBGRQ       | *1 |

| 16 | -   | GND         |    | 15 | O/D   | nSRST       | *2 |

| 14 | -   | GND         |    | 13 | OUT   | SWO         |    |

| 12 | -   | GND         |    | 11 | -     | (Pull Down) | *5 |

| 10 | -   | GND         |    | 9  | IN    | SWDCK       |    |

| 8  | -   | GND         |    | 7  | INOUT | SWDIO       |    |

| 6  | -   | GND         | *4 | 5  | -     | N.C.        |    |

| 4  | -   | GND.        |    | 3  | -     | N.C.        |    |

| 2  | -   | VSupply     | *3 | 1  | -     | VTref       | *3 |

I/O方向は、ユーザーシステム側(MPU)から見た入出力方向を示します。

● IN : ICE  $\rightarrow$  ユーザーシステム

●OUT : ユーザーシステム  $\rightarrow$  ICE  $\bullet$  INOUT : ユーザーシステム  $\Leftrightarrow$  ICE

- ●O/Dは、オープンドレインです。双方向信号となります。

- \*1 ご使用の MPU によってはアサインされていない場合があります。 『ユーザーシステムに必要な回路』『ユーザーシステム結線の注意事項』をご覧になり、指示に従い端子処理してください。

- \*2 オープンドレイン端子です。ユーザーシステム上の信号と WIRED-OR してください。

- \*3 ユーザーシステムの JTAG 信号の I/O 電源に接続してください。詳細は『ユーザーシステム結線の注意事項』 をご覧ください。

- \*4 ユーザーシステムの GND に必ず接続してください。

- \*5 コネクタ端子を 10KΩ程度でプルダウン処理してください。

- 6番 pin は、ICE のプローブが接続されていることを検知するために使用します。そのため、ユーザーシステム側で GND に接続しておく必要があります。

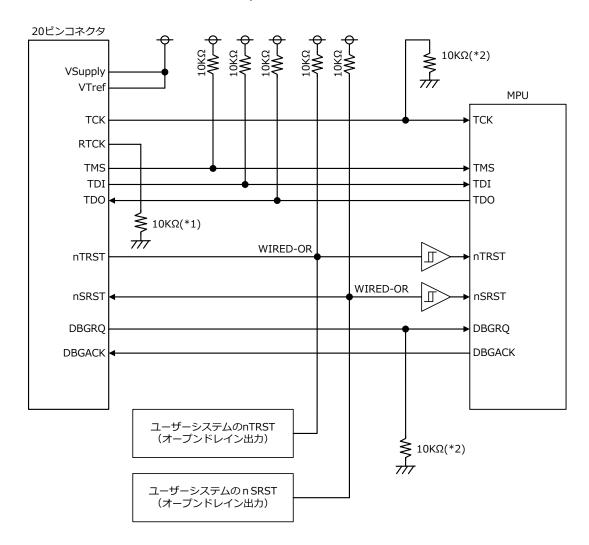

#### 2.1.4. ユーザーシステムに必要な回路

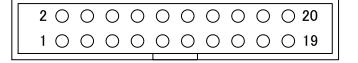

## ① CoreSight JTAG インターフェースの場合

- \*1 抵抗値は推奨値です。ユーザーシステムの特性に合わせて適切な抵抗値を選択してください。

- \*2 ご使用の MPU によっては、RTCK はアサインされていない場合があります。この場合はコネクタ端子を 10KΩ程度で プルダウン処理してください。

- \*3 ICE 未接続時に MPU が誤動作しないように、10KΩ程度の抵抗でプルダウンしてください。

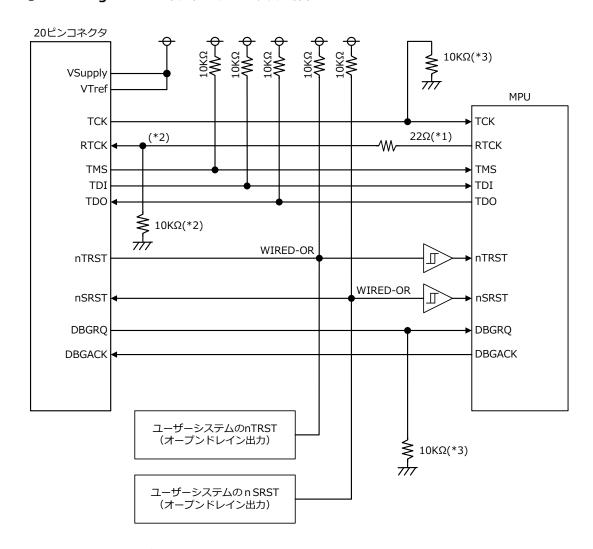

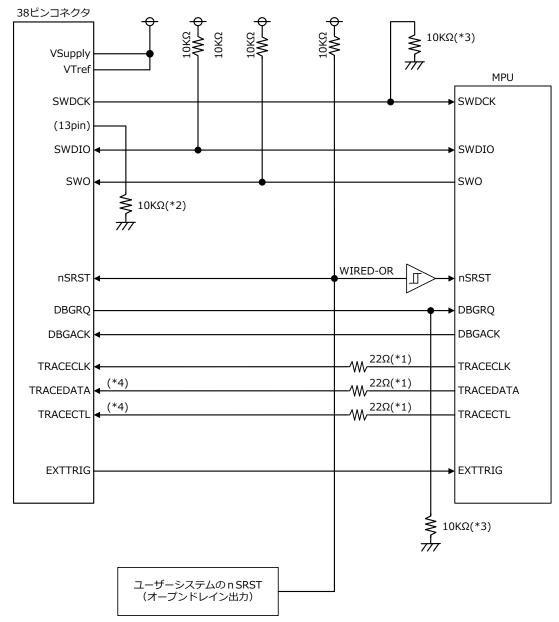

## ② CoreSight SWD インターフェースの場合

- \*1 コネクタ端子を 10KΩ程度でプルダウン処理してください。

- \*2 ICE 未接続時に MPU が誤動作しないように、10KΩ程度の抵抗でプルダウンしてください。

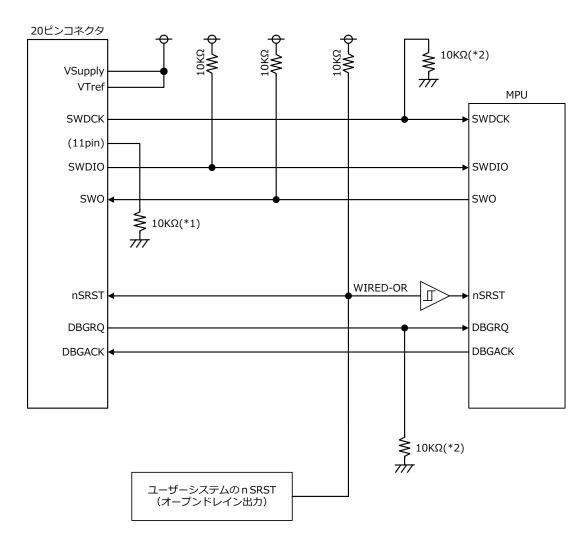

## ③ ソフトマクロコア(ARM7TDMI-S,ARM9E-S,ARM11 など)の場合

- \*1 抵抗値は推奨値です。ユーザーシステムの特性に合わせて適切な抵抗値を選択してください。

- \*2 ICE 未接続時に MPU が誤動作しないように、10KΩ程度の抵抗でプルダウンしてください。

## ④ ハードマクロコア(ARM7TDMI,ARM9TDMI など)の場合

- \*1 ハードマクロコアご使用時は、RTCK は 10K $\Omega$ 程度の抵抗でプルダウンしてください。

- \*2 ICE 未接続時に MPU が誤動作しないように、10KΩ程度の抵抗でプルダウンしてください。

# 2.2. 38 ピン ETM インターフェース(H2X600XP/HLX600TP)

## 2.2.1. 適合コネクタ

| インターフェース  | メーカー                      | 適合コネクタ               | 仕様          |  |  |  |             |  |

|-----------|---------------------------|----------------------|-------------|--|--|--|-------------|--|

| 38 ピン ETM | AMP                       | ストレートタイプ(金メッキ)       | Mictor シリーズ |  |  |  |             |  |

| インターフェース  | (I)===+                   | GND リード 1.4mm        | 0.635mm ピッチ |  |  |  |             |  |

|           | <代理店><br>  タイコエレクトロニクスアンプ | · 2-767004-2         | 38 ピンコネクタ   |  |  |  |             |  |

|           | 株式会社                      | · 2-5767004-2        |             |  |  |  |             |  |

|           |                           | ストレートタイプ (パラジウムニッケル) |             |  |  |  |             |  |

|           |                           | GND リード 2.74mm       |             |  |  |  |             |  |

|           |                           | · 767054-1           |             |  |  |  |             |  |

|           |                           |                      |             |  |  |  | • 5767054-1 |  |

|           |                           | ストレートタイプ(パラジウムニッケル)  |             |  |  |  |             |  |

|           |                           | GND リード 3.51mm       |             |  |  |  |             |  |

|           |                           | · 767061-1           |             |  |  |  |             |  |

|           |                           | · 5767061-1          |             |  |  |  |             |  |

|           |                           |                      |             |  |  |  |             |  |

#### 2.2.2. コネクタのピン配置図

① コネクタ実装面視

② 基板レイアウト

Standard Groud Bus Leads は、 GND に接続してください

#### 2.2.3. コネクタのピンアサイン

## ① CoreSight ETM, CoreSight JTAG インターフェースの場合

| ピン | I/O | Signal name  |    | ピン | I/O | Signal name   |    |

|----|-----|--------------|----|----|-----|---------------|----|

| 38 | OUT | TRACEDATA[0] |    | 37 | OUT | TRACEDATA[8]  | *1 |

| 36 | OUT | TRACECTL     | *2 | 35 | OUT | TRACEDATA[9]  | *1 |

| 34 | OUT | VDD          | *4 | 33 | OUT | TRACEDATA[10] | *1 |

| 32 | OUT | GND          |    | 31 | OUT | TRACEDATA[11] | *1 |

| 30 | OUT | GND          |    | 29 | OUT | TRACEDATA[12] | *1 |

| 28 | OUT | TRACEDATA[1] |    | 27 | OUT | TRACEDATA[13] | *1 |

| 26 | OUT | TRACEDATA[2] |    | 25 | OUT | TRACEDATA[14] | *1 |

| 24 | OUT | TRACEDATA[3] |    | 23 | OUT | TRACEDATA[15] | *1 |

| 22 | OUT | TRACEDATA[4] | *1 | 21 | O/D | nTRST         | *3 |

| 20 | OUT | TRACEDATA[5] | *1 | 19 | IN  | TDI           |    |

| 18 | OUT | TRACEDATA[6] | *1 | 17 | IN  | TMS           |    |

| 16 | OUT | TRACEDATA[7] | *1 | 15 | IN  | TCK           |    |

| 14 | -   | VSupply      | *4 | 13 | OUT | RTCK          | *5 |

| 12 | -   | VTref        | *4 | 11 | OUT | TDO           |    |

| 10 | IN  | EXTTRIG      | *2 | 9  | O/D | nSRST         | *3 |

| 8  | OUT | DBGACK       | *2 | 7  | IN  | DBGRQ         | *2 |

| 6  | OUT | TRACECLK     |    | 5  | -   | GND           |    |

| 4  | -   | N.C.         |    | 3  | -   | N.C.          |    |

| 2  | -   | N.C.         |    | 1  | -   | N.C.          |    |

I/O 方向は、ユーザーシステム側(MPU)から見た入出力方向を示します。

● IN : ICE → ユーザーシステム

●OUT : ユーザーシステム  $\rightarrow$  ICE  $\rightarrow$  INOUT : ユーザーシステム  $\leftrightarrow$  ICE

●O/Dは、オープンドレインです。双方向信号となります。

- \*1 未使用の TRACEDATA 信号は GND に接続してください。

- \*2 ご使用の MPU によってはアサインされていない場合があります。 『ユーザーシステムに必要な回路』『ユーザーシステム結線の注意事項』をご覧になり、指示に従い端子処理してください。

- \*3 オープンドレイン端子です。ユーザーシステム上の信号と WIRED-OR してください。

- \*4 ユーザーシステムの JTAG/ETM 信号の I/O 電源に接続してください。詳細は『ユーザーシステム結線の注意事項』をご覧ください。

- \*5 TCKのループバック信号です。『ユーザーシステムに必要な回路』『ユーザーシステム結線の注意事項』をご覧になり、指示に従い端子処理してください。

Doc.Rev. 2 Page 13 of 34

### ② CoreSight ETM, CoreSight SWD インターフェースの場合

| ピン | I/O | Signal name  |    | ピン | I/O   | Signal name   |    |

|----|-----|--------------|----|----|-------|---------------|----|

| 38 | OUT | TRACEDATA[0] |    | 37 | OUT   | TRACEDATA[8]  | *1 |

| 36 | OUT | TRACECTL     | *2 | 35 | OUT   | TRACEDATA[9]  | *1 |

| 34 | OUT | VDD          | *4 | 33 | OUT   | TRACEDATA[10] | *1 |

| 32 | OUT | GND          |    | 31 | OUT   | TRACEDATA[11] | *1 |

| 30 | OUT | GND          |    | 29 | OUT   | TRACEDATA[12] | *1 |

| 28 | OUT | TRACEDATA[1] |    | 27 | OUT   | TRACEDATA[13] | *1 |

| 26 | OUT | TRACEDATA[2] |    | 25 | OUT   | TRACEDATA[14] | *1 |

| 24 | OUT | TRACEDATA[3] |    | 23 | OUT   | TRACEDATA[15] | *1 |

| 22 | OUT | TRACEDATA[4] | *1 | 21 | -     | N.C.          |    |

| 20 | OUT | TRACEDATA[5] | *1 | 19 | -     | N.C.          |    |

| 18 | OUT | TRACEDATA[6] | *1 | 17 | INOUT | SWDIO         |    |

| 16 | OUT | TRACEDATA[7] | *1 | 15 | IN    | SWDCK         |    |

| 14 | -   | VSupply      | *4 | 13 | -     | (Pulldown)    | *5 |

| 12 | -   | VTref        | *4 | 11 | OUT   | SWO           |    |

| 10 | IN  | EXTTRIG      | *2 | 9  | O/D   | nSRST         | *3 |

| 8  | OUT | DBGACK       | *2 | 7  | IN    | DBGRQ         | *2 |

| 6  | OUT | TRACECLK     |    | 5  | -     | GND           |    |

| 4  | -   | N.C.         |    | 3  | -     | N.C.          |    |

| 2  | -   | N.C.         |    | 1  | -     | N.C.          |    |

I/O 方向は、ユーザーシステム側(MPU)から見た入出力方向を示します。

● IN : ICE → ユーザーシステム

●OUT : ユーザーシステム  $\rightarrow$  ICE  $\rightarrow$  INOUT : ユーザーシステム  $\leftrightarrow$  ICE

●O/Dは、オープンドレインです。双方向信号となります。

- \*1 未使用の TRACEDATA 信号は GND に接続してください。

- \*2 ご使用の MPU によってはアサインされていない場合があります。 『ユーザーシステムに必要な回路』『ユーザーシステム結線の注意事項』をご覧になり、指示に従い端子処 理してください。

- \*3 オープンドレイン端子です。ユーザーシステム上の信号と WIRED-OR してください。

- \*4 ユーザーシステムの JTAG/ETM 信号の I/O 電源に接続してください。詳細は『ユーザーシステム結線の注意事項』をご覧ください。

- \*5 コネクタ端子を 10KΩ程度でプルダウン処理してください。

#### ③ ARM7 / ARM9 コア (ETM 動作モード:Normal mode)の場合

| ピン | I/O | Signal name |    | ピン | I/O | Signal name  |    |    |

|----|-----|-------------|----|----|-----|--------------|----|----|

| 38 | OUT | PIPESTAT[0] |    | 37 | OUT | TRACEPKT[8]  | *1 | *2 |

| 36 | OUT | PIPESTAT[1] |    | 35 | OUT | TRACEPKT[9]  | *1 | *2 |

| 34 | OUT | PIPESTAT[2] |    | 33 | OUT | TRACEPKT[10] | *1 | *2 |

| 32 | OUT | TRACESYNC   |    | 31 | OUT | TRACEPKT[11] | *1 | *2 |

| 30 | OUT | TRACEPKT[0] |    | 29 | OUT | TRACEPKT[12] | *1 | *2 |

| 28 | OUT | TRACEPKT[1] |    | 27 | OUT | TRACEPKT[13] | *1 | *2 |

| 26 | OUT | TRACEPKT[2] |    | 25 | OUT | TRACEPKT[14] | *1 | *2 |

| 24 | OUT | TRACEPKT[3] |    | 23 | OUT | TRACEPKT[15] | *1 | *2 |

| 22 | OUT | TRACEPKT[4] | *2 | 21 | O/D | nTRST        | *4 |    |

| 20 | OUT | TRACEPKT[5] | *2 | 19 | IN  | TDI          |    |    |

| 18 | OUT | TRACEPKT[6] | *2 | 17 | IN  | TMS          |    |    |

| 16 | OUT | TRACEPKT[7] | *2 | 15 | IN  | TCK          |    |    |

| 14 | -   | VSupply     | *5 | 13 | OUT | RTCK         | *6 |    |

| 12 | -   | VTref       | *5 | 11 | OUT | TDO          |    |    |

| 10 | IN  | EXTTRIG     | *3 | 9  | O/D | nSRST        | *4 |    |

| 8  | OUT | DBGACK      | *3 | 7  | IN  | DBGRQ        | *3 |    |

| 6  | OUT | TRACECLK    |    | 5  | -   | GND          |    |    |

| 4  | -   | N.C.        |    | 3  | -   | N.C.         |    |    |

| 2  | -   | N.C.        |    | 1  | -   | N.C.         |    |    |

I/O 方向は、ユーザーシステム側(MPU)から見た入出力方向を示します。

● IN : ICE  $\rightarrow$  ユーザーシステム

●OUT : ユーザーシステム → ICE

●O/Dは、オープンドレインです。双方向信号となります。

- \*1 TRACEPKT 信号8本の場合、未接続、またはGND に接続してください。

- \*2 TRACEPKT 信号 4 本の場合、未接続、または GND に接続してください。

- \*3 ご使用の MPU によってはアサインされていない場合があります。

『ユーザーシステムに必要な回路』『ユーザーシステム結線の注意事項』をご覧になり、指示に従い端子処理してください。

- \*4 オープンドレイン端子です。ユーザーシステム上の信号と WIRED-OR してください。

- \*5 ユーザーシステムの JTAG/ETM 信号の I/O 電源に接続してください。詳細は『ユーザーシステム結線の注意事項』をご覧ください。

- \*6 TCKのループバック信号です。『ユーザーシステムに必要な回路』『ユーザーシステム結線の注意事項』をご覧になり、指示に従い端子処理してください。

Doc.Rev. 2 Page 15 of 34

#### ④ ARM11コアの場合

| ピン | I/O | Signal name  |    | ピン | I/O | Signal name   |    |

|----|-----|--------------|----|----|-----|---------------|----|

| 38 | OUT | TRACEDATA[0] |    | 37 | OUT | TRACEDATA[8]  | *1 |

| 36 | OUT | TRACECTL     |    | 35 | OUT | TRACEDATA[9]  | *1 |

| 34 | OUT | VDD          | *4 | 33 | OUT | TRACEDATA[10] | *1 |

| 32 | OUT | GND          |    | 31 | OUT | TRACEDATA[11] | *1 |

| 30 | OUT | GND          |    | 29 | OUT | TRACEDATA[12] | *1 |

| 28 | OUT | TRACEDATA[1] |    | 27 | OUT | TRACEDATA[13] | *1 |

| 26 | OUT | TRACEDATA[2] |    | 25 | OUT | TRACEDATA[14] | *1 |

| 24 | OUT | TRACEDATA[3] |    | 23 | OUT | TRACEDATA[15] | *1 |

| 22 | OUT | TRACEDATA[4] | *1 | 21 | O/D | nTRST         | *3 |

| 20 | OUT | TRACEDATA[5] | *1 | 19 | IN  | TDI           |    |

| 18 | OUT | TRACEDATA[6] | *1 | 17 | IN  | TMS           |    |

| 16 | OUT | TRACEDATA[7] | *1 | 15 | IN  | TCK           |    |

| 14 | -   | VSupply      | *4 | 13 | OUT | RTCK          | *5 |

| 12 | -   | VTref        | *4 | 11 | OUT | TDO           |    |

| 10 | IN  | EXTTRIG      | *2 | 9  | O/D | nSRST         | *3 |

| 8  | OUT | DBGACK       | *2 | 7  | IN  | DBGRQ         | *2 |

| 6  | OUT | TRACECLK     |    | 5  | -   | GND           |    |

| 4  | -   | N.C.         |    | 3  | -   | N.C.          |    |

| 2  | -   | N.C.         |    | 1  | -   | N.C.          |    |

I/O 方向は、ユーザーシステム側(MPU)から見た入出力方向を示します。

● IN : ICE → ユーザーシステム

● OUT : ユーザーシステム → ICE

●O/Dは、オープンドレインです。双方向信号となります。

- \*1 未使用の TRACEDATA 信号は GND に接続してください。

- \*2 ご使用の MPU によってはアサインされていない場合があります。 『ユーザーシステムに必要な回路』『ユーザーシステム結線の注意事項』をご覧になり、指示に従い端子処理してください。

- \*3 オープンドレイン端子です。ユーザーシステム上の信号と WIRED-OR してください。

- \*4 ユーザーシステムの JTAG/ETM 信号の I/O 電源に接続してください。詳細は『ユーザーシステム結線の注意事項』をご覧ください。

- \*5 TCKのループバック信号です。『ユーザーシステムに必要な回路』『ユーザーシステム結線の注意事項』をご覧になり、指示に従い端子処理してください。

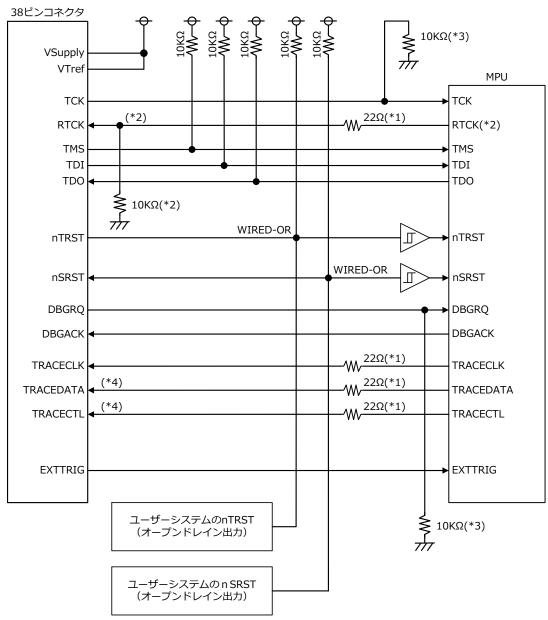

#### 2.2.4. ユーザーシステムに必要な回路

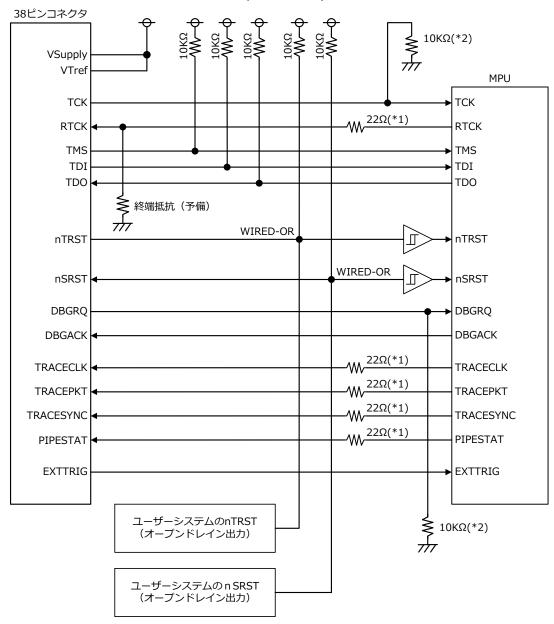

① CoreSight ETM, CoreSight JTAG インターフェースの場合

- \*1 抵抗値は推奨値です。ユーザーシステムの特性に合わせて適切な抵抗値を選択してください。

- \*2 ご使用の MPU によっては、RTCK はアサインされていない場合があります。この場合はコネクタ端子を 10KΩ程度で プルダウン処理してください。

- \*3 ICE 未接続時に MPU が誤動作しないように、10KΩ程度の抵抗でプルダウンしてください。

- \*4 ご使用になる ETM 設定に応じて端子処理を行ってください。

## ② CoreSight ETM, CoreSight SWD インターフェースの場合

- \*1 抵抗値は推奨値です。ユーザーシステムの特性に合わせて適切な抵抗値を選択してください。

- \*2 コネクタ端子を10ΚΩ程度でプルダウン処理してください。

- \*3 ICE 未接続時に MPU が誤動作しないように、10KΩ程度の抵抗でプルダウンしてください。

- \*4 ご使用になる ETM 設定に応じて端子処理を行ってください。

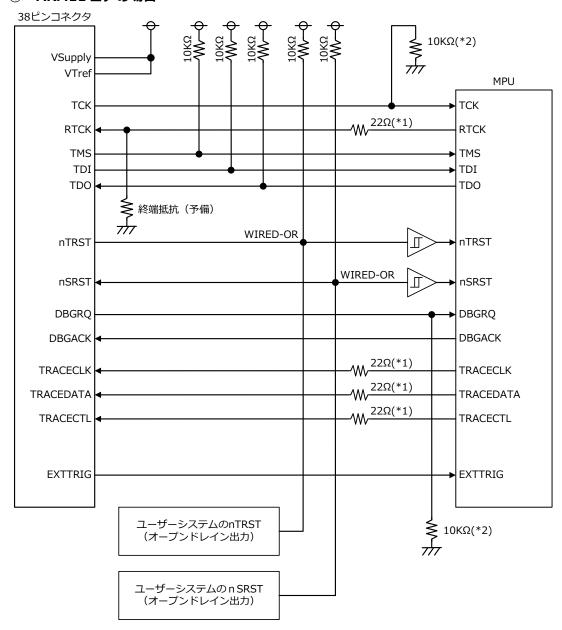

## ③ ソフトマクロコア(ARM7TDMI-S, ARM9E-S,ARM11 など)の場合

- \*1 抵抗値は推奨値です。ユーザーシステムの特性に合わせて適切な抵抗値を選択してください。

- \*2 ICE 未接続時に MPU が誤動作しないように、10KΩ程度の抵抗でプルダウンしてください。

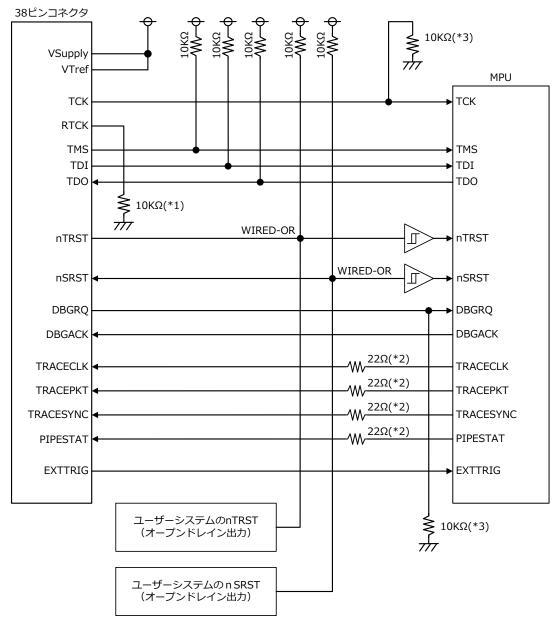

#### ④ ARM11コアの場合

- \*1 抵抗値は推奨値です。ユーザーシステムの特性に合わせて適切な抵抗値を選択してください。

- \*2 ICE 未接続時に MPU が誤動作しないように、10KΩ程度の抵抗でプルダウンしてください。

## ⑤ ハードマクロコア(ARM7TDMI, ARM9TDMI など)の場合

- \*1 ハードマクロコアご使用時は、RTCK は 10K $\Omega$ 程度の抵抗でプルダウンしてください。

- \*2 抵抗値は推奨値です。ユーザーシステムの特性に合わせて適切な抵抗値を選択してください。

- \*3 ICE 未接続時に MPU が誤動作しないように、10KΩ程度の抵抗でプルダウンしてください。

## 2.3. 14 ピン JTAG インターフェース(AE221)

## 2.3.1. 適合コネクタ

| インターフェース               | メーカー  | 適合コネクタ                                              | 仕様                                                    |

|------------------------|-------|-----------------------------------------------------|-------------------------------------------------------|

| 14 ピン JTAG<br>インターフェース | ヒロセ電機 | ライトアングル ・HIF3FC-14PA-2.54DS ・HIF3FC-14PA-2.54DS(71) | 2.54mm ピッチピンヘッダ<br>DIP タイプ 14 ピン<br>(Embedded-ICE 準拠) |

|                        |       | • HIF3FC-14PA-2.54DSA • HIF3FC-14PA-2.54DSA(71)     |                                                       |

## 2.3.2. コネクタのピン配置図

コネクタ実装面視

#### 2.3.3. コネクタのピンアサイン

| ピン | I/O | Signal name |    | ピン | I/O | Signal name |    |

|----|-----|-------------|----|----|-----|-------------|----|

| 14 | -   | GND         |    | 13 | -   | VSupply     | *2 |

| 12 | O/D | nSRST       | *1 | 11 | OUT | TDO         |    |

| 10 | -   | GND         |    | 9  | IN  | TCK         |    |

| 8  | -   | GND         |    | 7  | IN  | TMS         |    |

| 6  | -   | GND         | *3 | 5  | IN  | TDI         |    |

| 4  | -   | GND.        |    | 3  | O/D | nTRST       | *1 |

| 2  | -   | GND         |    | 1  | -   | VTref       | *2 |

I/O方向は、ユーザーシステム側(MPU)から見た入出力方向を示します。

● IN : ICE → ユーザーシステム

●OUT : ユーザーシステム  $\rightarrow$  ICE  $\bullet$  INOUT : ユーザーシステム  $\Leftrightarrow$  ICE

●O/Dは、オープンドレインです。双方向信号となります。

- \*1 オープンドレイン端子です。ユーザーシステム上の信号と WIRED-OR してください。

- \*3 ユーザーシステムの JTAG 信号の I/O 電源に接続してください。詳細は『ユーザーシステム結線の注意事項』 をご覧ください。

- \*3 ユーザーシステムの GND に必ず接続してください。

- **リフトマクロコアをご使用の場合、14 ピン JTAG インターフェースでは接続できません。**

- 6番 pin は、ICE のプローブが接続されていることを検知するために使用します。 そのため、ユーザーシステム側で GND に接続しておく必要があります。

- 14 ピン JTAG インターフェースでは、CoreSight SWD インターフェースを サポートしていません。

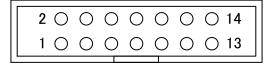

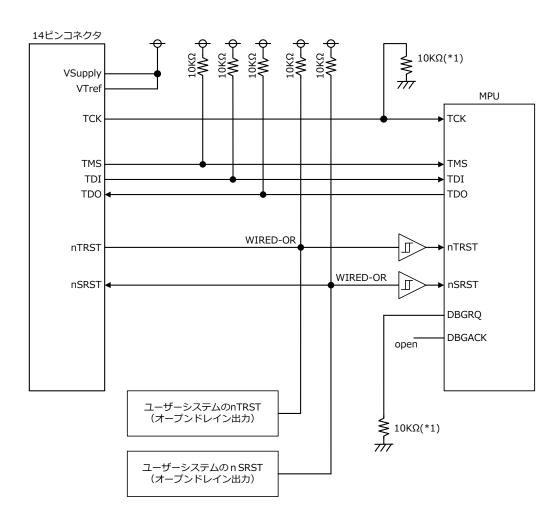

#### 2.3.4. ユーザーシステムに必要な回路

\*1 ICE 未接続時に MPU が誤動作しないように、10KΩ程度の抵抗でプルダウンしてください。

## 2.4. 20-14 ピン Xtensa 純正 ICE 準拠インターフェース(AE729)

## 2.4.1. 適合コネクタ

| インターフェース                                 | メーカー        | 適合コネクタ                    | 仕様                                                     |

|------------------------------------------|-------------|---------------------------|--------------------------------------------------------|

| 20-14 ピン<br>Xtensa 純正 ICE 準拠<br>インターフェース | 日本航空電子(JAE) | ストレート<br>・PS14PF-D4T1-PKL | 2.54mm ピッチピンヘッダ<br>DIP タイプ 14 ピン<br>(Xtensa 純正 ICE 準拠) |

## 2.4.2. コネクタのピン配置図

コネクタ実装面視

8 ピンは、プローブ誤挿入防止のため、プローブ側では穴詰めしています。 ユーザーシステム側コネクタでは、ピンを取り除いてください。

## 2.4.3. コネクタのピンアサイン

| ピン | I/O | Signal name |     | ピン | I/O | Signal name |    |

|----|-----|-------------|-----|----|-----|-------------|----|

| 14 | O/D | /TRST       | *1  | 13 | -   | N.C.        | *4 |

| 12 | -   | N.C.        | *4  | 11 | -   | VccIO       | *2 |

| 10 | IN  | TMS         |     | 9  | O/D | /RESET      | *1 |

| 8  | -   | N.C.(KEY)   | *3  | 7  | -   | N.C.        | *4 |

| 6  | -   | GND         |     | 5  | IN  | TCK         |    |

| 4  | -   | GND         | GND |    | OUT | TDO         |    |

| 2  | -   | GND         | *5  | 1  | IN  | TDI         |    |

I/O 方向は、ユーザーシステム側(MPU)から見た入出力方向を示します。

● IN : ICE → ユーザーシステム

●OUT : ユーザーシステム → ICE

●O/Dは、オープンドレインです。双方向信号となります。

- \*1 オープンドレイン端子です。ユーザーシステム上の信号と WIRED-OR してください。

- \*2 ユーザーシステムの JTAG 信号の I/O 電源に接続してください。

- \*3 コネクタ逆挿し防止用の KEY です。N.C. (オープン) としてください。 8 ピンは、プローブ誤挿入防止のため、プローブ側は穴詰めしています。 ユーザーシステム側コネクタでは、ピンを取り除いてください。

- \*4 N.C.の端子には、何も接続しないでください。

- \*5 必ず GND に接続してください。

#### 2.4.4. ユーザーシステムに必要な回路

#### 2.5. ユーザーシステム結線の注意事項

ユーザーシステムボードの設計においては、下記の注意事項にご配慮ください。 各信号が正しく接続されないと ICE は正常動作しなくなることがあります。

#### nSRST 信号について

nSRST 信号は、ICE 側で MPU のリセット信号の制御及び、リセットの監視に使用します。 ICE から出力される nSRST 信号は、オープンドレイン出力です。 プルアップあり(電源: VTref) / プルアップなし を選択できます。

通常は、以下の条件でご使用ください。

| nSRST と VTref の関係                   | プルアップ条件の設定                       |

|-------------------------------------|----------------------------------|

| nSRST 信号が VTref と同じ電源系の場合           | プルアップありを選択する。                    |

| nSRST 信号が VTref と異なる電源系の場合          | プルアップなしを選択する。                    |

| 例: VTref=+1.8V。nSRST 信号は+3.3V のシステム | +3.3V から VTref(+1.8V)への電流リークが発生し |

| 電源系に接続されている場合                       | ません。                             |

オープンドレイン出力で正常動作できるよう、以下の点にご注意ください。

- ユーザーシステムボード上でボードのリセット信号と WIRED-OR してください。

- ユーザーシステムボードのリセット回路もオープンドレイン出力としてください。

- ユーザーシステムボード上で必ずプルアップ処理してください。

ICE からの nSRST 出力は、ユーザーシステムボード上でシュミット・トリガ IC に入力してください。(MPU の入力端子がシュミット入力であれば、シュミット・トリガ IC は不要です。) シュミット・トリガ IC 以外に入力された場合、誤動作の原因となる場合があります。

### ② nTRST 信号について

nTRST 信号は JTAG 及び、MPU 内蔵デバッグ資源のリセット信号です。

ICE 動作時にユーザーシステム上から nTRST 信号をアサート(L)されますと MPU のデバッグ制御システムが初期化され、正常にデバッグできなくなります。

ユーザーシステムでの nTRST はパワーオン時のみアサートするようにしてください。

ICE からの nTRST 出力はオープンドレイン出力、またはバッファドライブ出力のどちらかを選択可能です(初期状態はオープンドレイン出力になっています)。通常はオープンドレイン出力でご使用ください。

オープンドレイン出力で正常動作できるよう、以下の点にご注意ください。

- ユーザーシステムボード上でユーザーシステムの nTRST 信号と WIRED-OR してください

- ユーザーシステムボードのリセット回路もオープンドレイン出力としてください。

- ユーザーシステムボード上で必ずプルアップ処理してください

Doc.Rev. 2 Page 28 of 34

バッファドライブ方式を使用する場合、ユーザーシステム上での信号の衝突にご注意ください。

オープンドレイン方式では正常動作しない場合 (例:nTRST 信号がユーザーシステムでプルダウンされている)、バッファドライブ方式を選択することで、正常動作させることができます。

ただしバッファドライブ方式を選択する場合、ユーザーシステム上のリセット信号と衝突が発生しないよう、ユーザーシステムのリセット回路構成に注意が必要です。

信号衝突によりユーザーシステム及び ICE を破損する場合がありますのでご注意ください。

ICE からの nTRST 出力は、ユーザーシステムボード上でシュミット・トリガ IC に入力してください。(MPU の入力端子がシュミット入力であれば、シュミット・トリガ IC は不要です。)シュミット・トリガ IC 以外に入力された場合、誤動作の原因となる場合があります。

③ ソフトウェアリセットもしくは MPU の内部モジュールによるリセットがある MPU について ICE では、デバッグ機能の実現のため、ユーザーシステム上の MPU のリセット端子を監視しています。 ソフトウェアリセットまたは、内部モジュールによるリセット機能によるリセット発生時、ICE は MPU のリセット入力端子を監視していますので、MPU リセット発生が正しく検知できません。

#### ④ DBGRQ 信号

ご使用のMPUによっては、外部ピンにアサインされていない場合があります。

DBGRQ 信号がアサインされていない MPU の場合、JTAG インターフェース・コネクタ、ETM インターフェース・コネクタの DBGRQ 端子はオープンとしてください。

なお、ICE を接続しない場合、DBGRQ 信号は Low レベル固定にする必要があります。ユーザーシステム上でプルダウン処理等の配慮を行います。

#### ⑤ DBGACK 信号

ご使用の MPU によっては、外部ピンにアサインされていない場合があります。 DBGACK 信号がアサインされていない MPU の場合、JTAG インターフェース・コネクタ、ETM インターフェース・コネクタの DBGACK 端子は**プルダウン処理(10KΩ)**してください。

#### ⑥ RTCK 信号

### ARM ソフトマクロコアにおいて、JTAG 通信を行う際の同期信号となります。

ソフトマクロコア(ARM7TDMI-S,ARM9E-S,ARM11 など)ご使用時は、必ず MPU の RTCK 端子と接続してください。RTCK が接続されない場合、MPU と ICE との通信が不安定になることがあります。

ASIC 設計時には、ICE 接続での安定性確保のため、RTCK をピン出力していただくことを強く推奨いたします。

ハードマクロコアでは、RTCK は存在しないため、JTAG インターフェース・コネクタ、ETM インターフェース・コネクタの RTCK 端子は**プルダウン処理(10KΩ)**してください。

RTCK 信号波形にノイズ成分が発生すると ICE の誤動作を招きます。

RTCK ラインへのダンピング抵抗、終端抵抗等による波形成形を推奨いたします。

終端抵抗は通常必要ありませんが、波形品質が劣化している場合に有効な場合がありますので、

実装できるようにご配慮いただくことを推奨いたします。

#### (7) VTref

JTAG 信号、ETM 信号のロジックレベル基準電圧として使用します。

ユーザーシステムの、JTAG 信号、ETM 信号の I/O 電源に接続してください。

VTref 端子は、プルアップ処理など抵抗を介した接続ではなく、直接電源に接続することを推奨します。

抵抗を介して接続する場合、ICE 内部のプルダウン抵抗(約  $100 \mathrm{K}\Omega$ )による電圧降下が問題とならないように  $1 \mathrm{K}\Omega$ 以下の抵抗値としてください。

#### 8 VSupply

VSupply は、ユーザーシステムからの電源供給を必要とする機器のために用意されています。

VSupply は、ICE では使用していません。

従って未接続でも構いませんが、他のデバッグ機器との互換性の点から、VTref 端子と同じ電源を接続することを推奨します。

ICE 以外の機器を接続する必要がある場合は、そちらの規定に従った処理をしてください。

### ⑨ TMS,TCK の処理について

TMS,TCK は ICE を接続しないときに JTAG の不正なステート遷移を禁止するために、端子処理が必要な場合があります。

端子処理(プルアップ、プルダウン等)は MPU 端子の内部処理プルアップ、プルダウン等の有無により処理が異なりますので、MPU のマニュアルをご覧のうえ適切な処理を行ってください。

#### ⑩ EXTTRIG 信号(トレースモデルご使用の場合)

ICE からのトリガ出力です。ETM のトリガ入力に接続します。

本信号は現バージョンではサポートしていません。

#### ① VDD

VDD は、ICE では使用していません。

従って未接続でも構いませんが、他のデバッグ機器との互換性の点から、VDD 端子は、ロジックレベルが 1 になるように、VTref 端子と同じ電源に接続するか、10KΩ程度の抵抗でプルアップすることを推奨します。

#### 迎 ETM 信号

ETM 信号(\*1)は MPU コアクロックに同期して出力される高速信号です。ユーザーシステム基板設計時、下記点にご配慮ください。

- a) ETM 信号ラインの特性インピーダンスが 50Ω になるようにパターン設計してください。

- b) ETM 信号間のスキューが発生しないよう、コネクタまで等長配線してください。

- c) ETM 信号ラインは最短となるよう、ETM プローブインターフェースコネクタはユーザーシステムチップの 近傍に配置してください。

- d) ETM 信号出力バッファの出力インピーダンスと、基板特性インピーダンスとのミスマッチによる反射を発生させないよう、ETM 出力の近傍にダンピング抵抗を挿入してください。

#### \*1 ETM 信号

| ETM v1.x の場合 | TRACEPKT[15:0]  |

|--------------|-----------------|

|              | PIPESTAT[2:0]   |

|              | TRACESYNC       |

|              | TRACECLK        |

| ETM v3.x の場合 | TRACEDATA[15:0] |

|              | TRACECTL(*2)    |

|              | TRACECLK        |

\*2 ご使用の MPU によってはアサインされていない場合があります。 『38 ピン ETM インターフェース』をご覧になり、指示に従い端子処理してください。

**Q**

20 ピン/14 ピン JTAG インターフェースのみでの接続時は、イベント機能、トレース機能は、使用できません。

# 3. 補足事項

## 3.1. 適合コネクタについて

本書に記載されている適合コネクタは、あくまで一例であり、異なる型番のものや他のメーカー品でも適合可能なものも存在します。

本書に記載していないコネクタを使用する場合は、コネクタ仕様を確認の上、適合性を確認して下さい。

## 3.2. ユーザーシステムに必要な回路について

本書に記載されているユーザーシステムに必要な回路は、実際の回路図から未実装部品やその周辺回路など機能そのものに直接影響を与えない部分を削除した形で記載されています。

# 4. 参考資料

- 「adviceLUNA II ユーザーズマニュアル(共通編) AP520/AP521」 (adviceLUNA II \_podm\_jpn.pdf)

- •「adviceLUNA II ユーザーズマニュアル(固有編) H2X600」 (H2X600\_podm\_jpn.pdf)

- 「adviceLUNA ユーザーズマニュアル(共通編) AP510/AP511/AP512/AP514」 (adviceLUNA\_podm\_jpn.pdf)

- 「adviceLUNA ユーザーズマニュアル(固有編) HLX600」 (HLX600\_podm\_jpn.pdf)

# 改訂履歴

| 版   | 発行日付       | 変更内容  |

|-----|------------|-------|

| 第1版 | 2014.09.03 | 新規発行  |

| 第2版 | 2017.04.01 | 新商号対応 |

|     |            |       |