1.はじめに

前回の技術ブログではRISC-V ISA、およびRISC-V Core IPについて改めて解説しました。そして、RISC-V Core IPに対応したSoCジェネレータについてご説明し、SoCジェネレータの中でも手軽に利用できそうなLitexについてご紹介しました。

Litexを使うことで、対象とするCore IP、RISC-Vを32ビットモード(RV32)、あるいは64ビットモード(RV64)のどちらで動作させるのか、シングルコアなのかマルチコアなのか、何コア用意するのか、といった選択を容易に行うことができます。とは言え、初めてLitexを使う方、あるいは初めてFPGAに触れる方にとってはハードルが高いものです。今回はLitexを使って作成したSoCを簡単に試すことを目的として、すでにLitexを使って作成されたビットストリームデータ(※1)を入手し、それをFPGAに書き込み、RISC-V CPUの動作確認を行うところまでの手順をご紹介したいと思います。

※1 FPGAのコンフィグレーションに用いるデータのことをビットストリームデータと呼びます。FPGAにロジックを構築するための情報だけでなく、その上で動作するプログラムも含めることができます。

2.環境構築

LitexでサポートされるFPGAボードはこちらに示されるように様々なものがありますが、今回は本技術ブログでも過去に何度か登場しているDigilent社製Arty A7-100Tボードを用いることにします。

2.1.用意するもの

環境構築を行う上で用意したものを以下に挙げます(※2)。

- ハードウェア

ノートPC(CPU:Core i7-1185G7, RAM:16GB, SSD:512GB(空き領域:150GB))

Digilent社製Arty A7-100Tボード

USBケーブル(Type-A – micro-B) - ソフトウェア

Windows 10 Pro(バージョン:22H2, OSビルド:19045.2364)

Digilent社製Adeptアプリケーション(Revision:May 28.2010)

Tera Term(バージョン:4.106) - FPGAデータ

Arty A7-100Tボード用ビットストリームデータ(Prebuildイメージ)

※2 インターネット接続ができることを前提としており、そのための設備、環境についての説明は省きます。

2.2.Tera Termのインストール

Tera Termを使うと、Arty A7-100TボードからUSB経由で送られるシリアル出力メッセージをPC上で確認することができます。Arty A7-100TでRISC-V CPU上のプログラムが起動した際、動作結果を確認するために使用します。こちらよりTera Termの最新版を入手しインストールします。

2.3.Digilent社製Adeptアプリケーションのインストール

Arty A7-100TはAMD社(旧Xilinx社)製FPGAを搭載しています。AMD社製FPGAに対するビットストリームデータの書き込みは、一般的にはVivadoと呼ばれるAMD社が提供しているツールを用いられることが多いです。しかしながらVivadoは非常に多機能であることから操作に慣れが必要であり、さらに数GB以上のストレージを消費することから、今回は手軽に試せる手段として、Digilent社が提供しているAdeptアプリケーションを採用することとしました。Adeptアプリケーションの操作は非常にシンプルで、かつインストール後のサイズは1MB以内に収まります。このツールを使うと、Arty A7-100Tボード上のSRAMへのビットストリームデータの書き込み、FPGAにロジックを構築、実行させることができます。Adeptアプリケーションは、こちらで入手しインストールします。

2.4.Arty A7-100Tボード用ビットストリームデータのダウンロード

Arty A7-100Tボードで手軽に試すことができるビットストリームデータは、こちらにあるものを使用します。これは以前本ブログでもご紹介したRustで作られたRTOSであるTockをArty A7-100Tボード上に実装したRISC-V CPU(VexRiscv)で動かすために用意されたもので、Litexを用いて作成されているため今回活用することにしました。digilent_arty_a7-100t.zipをダウンロード、展開後にできる、”gateway\digilent_arty.bit”というファイルを使用します。

2.5.Arty A7-100Tボードの起動

Arty A7-100TボードはUSB給電に対応しています。PCをUSBケーブルで接続することで、PCからArty A7-100Tボードに電力供給され、PC上ではArty A7-100Tとシリアル通信を行うためのCOMポート番号が割り当てられます。

2.6.Tera Termの起動

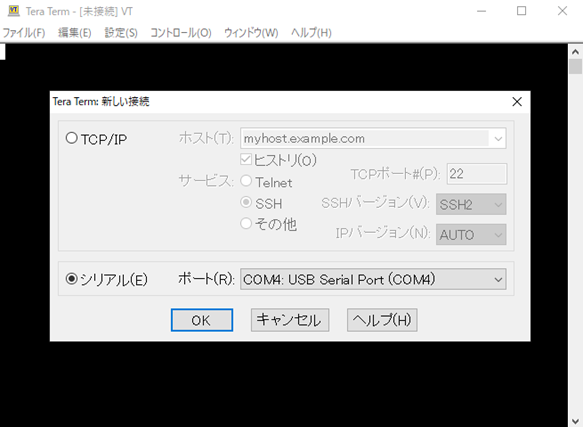

Tera Termを起動し、[ファイル]メニューより [新しい接続…]を選択します。正しくArty A7-100Tボードが認識されていると、下図のように対象となるCOMポートを選択することができます(※3)。[シリアル]を選択後、[OK]ボタンを押下します。

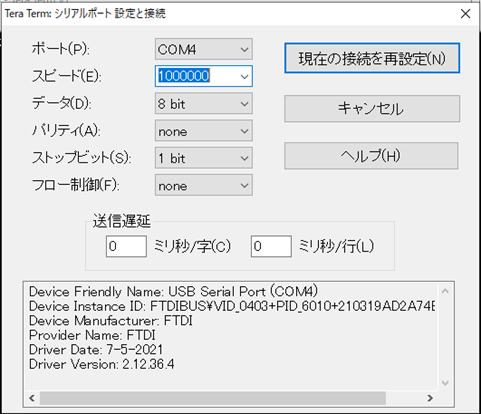

次に、[設定]メニューより、[シリアルポート…]を選択し、[シリアルポート設定と接続]ダイアログを開きます。 [スピード]の入力フィールドに、”1000000”を入力後、[現在の接続を再設定]ボタンを押下します。

※3 図ではCOM4を示していますが、番号は一定ではありません。

3.Arty A7-100TボードでRISC-V CPUを起動する

ここまでで一通りの準備が整いました。いよいよ、ビットストリームデータをArty A7-100Tボードへ書き込み、RISC-V CPUの起動を確認します。

3.1.ビットストリームデータの書き込み

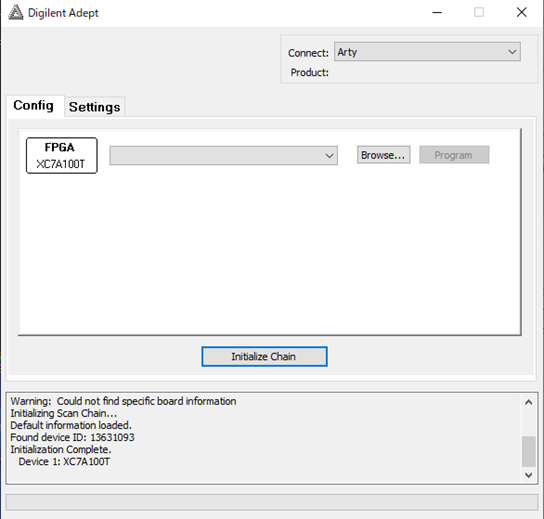

前章でインストール済みのAdeptアプリケーションを起動します。正しくArty A7-100Tボードが接続されていると、下図のような表示になります。

[Browse…]ボタンを押下して、ダウンロード済みのビットストリームデータ”gateway\digilent_arty.bit”を選択し、[Program]ボタンを押下します。

3.2.RISC-V CPUの起動

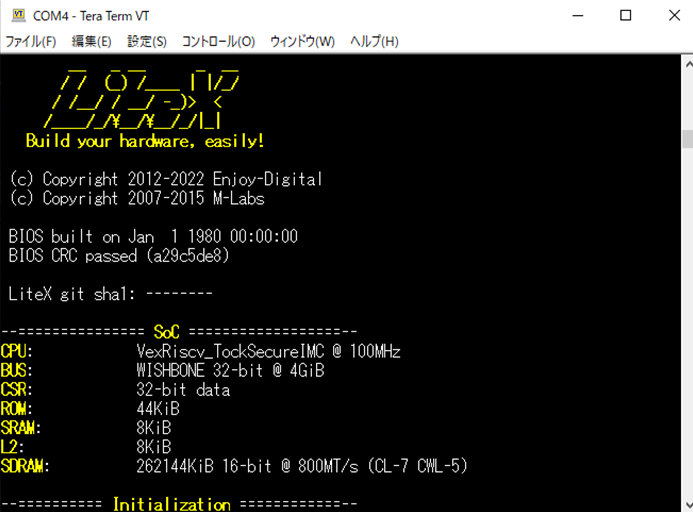

しばらく待つとビットストリームデータの書き込みが完了し、Tera Term上には下図のようなメッセージが表示されます。

RISC-V CPU(VexRiscv)が起動した後、その上でビットストリームデータに含まれるプログラムが起動し、シリアル出力によってTera Term上にメッセージが出力されます。このメッセージの内容から、今回FPGAに書き込みを行ったSoCがどのようなIPで構成されているのか、その一部を知ることができます。

4.まとめ

いかがでしたでしょうか。今回はお手軽にLitexを試すべく、すでにLitexを使ってSoC構築済みのビットストリームデータを入手し、Adeptアプリケーションを使ってFPGAに書き込み、RISC-V CPUが実際に動作するところまでをご紹介しました。すでに用意されているビットストリームデータを使うことで、とても簡単にRISC-V CPUをFPGA上で動作させることができる点をお伝えできたなら幸いです。 次回は、Litexを使ってSoCを構築する方法についてご紹介したいと思います。

本ブログについてのより詳しい内容のご質問は、こちらまでお問合せください。

info-lsi@dts-insight.co.jp

著作権および商標

その他、本ブログに記載する製品名は、一般に各開発メーカーの商標または登録商標です。

なお、本文中には™ および ® マークは表記していません。

■■DTSインサイトの「システムLSI設計ソリューションサービス」■■

DTSインサイトでは、システムLSI/FPGA設計の受託も行っています。

当社のノウハウを活かした、ソフトウェアの移行(マイグレーション)

サービスも提供しておりますので、お気軽にご相談ください。

システムLSI設計ソリューションサービス紹介は こちら