1.はじめに

DTSインサイトでHiFive Unmatchedボードを日本国内最速で入手できたことから、急きょRISC-V技術ブログ連載第4回、RISC-V技術ブログ連載第5回はHiFive Unmatchedボードのご紹介記事とさせていただきました。

今回は、RISC-V技術ブログ連載第3回「FPGAボード上でSiFive RISC-V Core を動かす① 」 の続編として、SiFive社が提供するソフトウェア統合開発環境(Freedom Studio)を用いて、プログラムをビルドし、FPGAボード上で実行、デバッグする方法をご紹介します。

2.環境準備

まず、RISC-V技術ブログ連載第3回でご説明したハードウェア接続を実施した上で、以下を行っていきます。

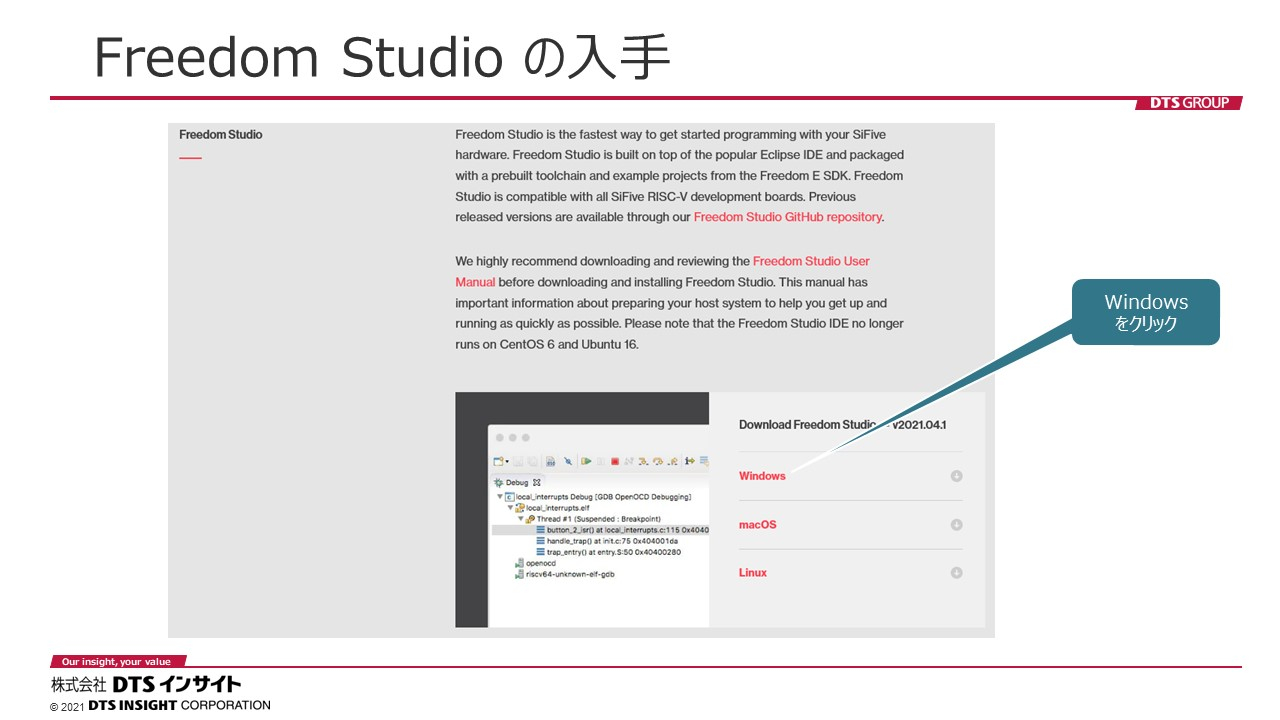

2.1.Freedom Studioのインストール

RISC-V技術ブログ連載第3回執筆時は、Freedom Studioのバージョンはv2020.11.0でした。

現在、新たにバージョンv2021.04.1が提供されていますので、今回は改めてこちらをインストールします。

こちら(https://www.sifive.com/software)よりWindows版を入手します。

ダウンロードしたzipファイルは、”c:¥FreedomStudio”フォルダを作成し、そこに展開してください。

2.2.ターミナルソフトのインストール

以下の設定が可能なターミナルソフトをインストールします。

- ボーレート(スピード):115200

- データ長:8bit

- パリティ:none

- ストップビット:1bit

- ストップビット:1bit

- フロー制御:none

- 改行コード:LF (※1)

※1 今回使用するFreedom Studioのversionでは、マルチプラットフォームに対応するため、受信の改行コードをLFとしています。

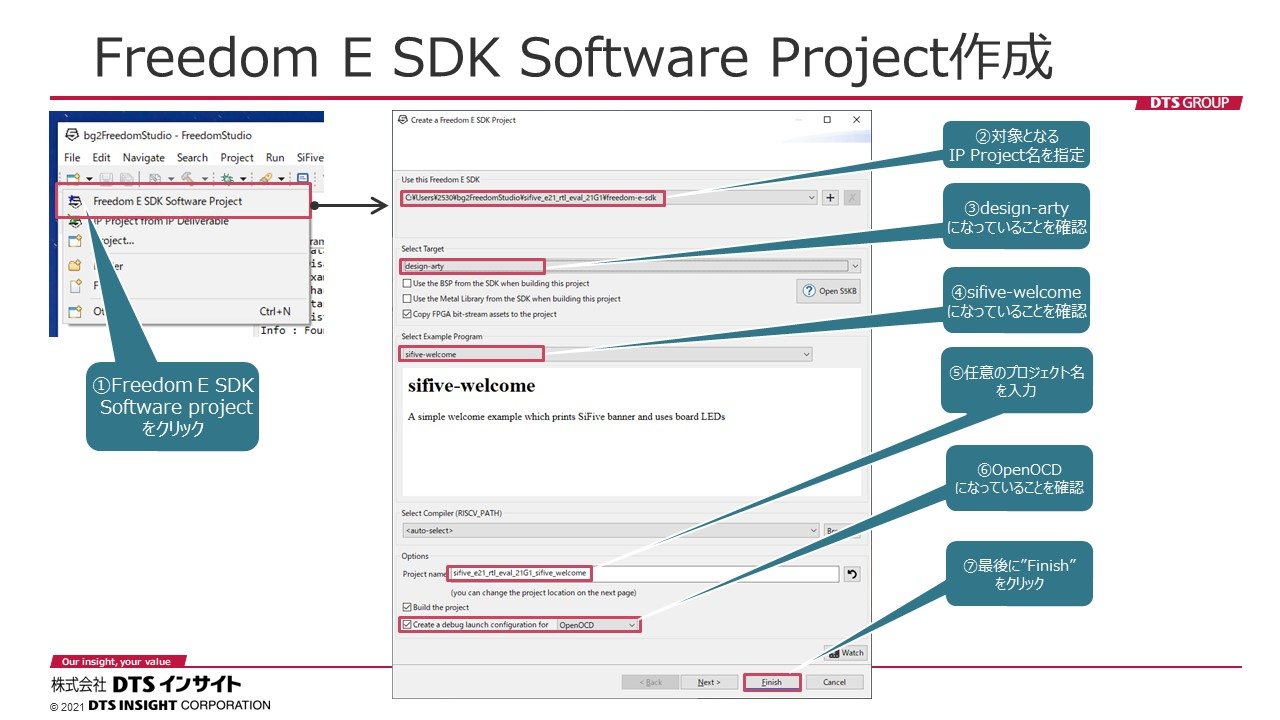

3.Freedom E SDK Software Project作成

Freedom Studioを起動し、Freedom E SDK(※2)を利用したサンプルプログラムを作成します。

まず、FPGA上で実行するソフトウェアに対応したプロジェクト(Freedom E SDK Software Project)を作成します。

上図の様にプロジェクトの作成を進め、最後に “Finish” をクリックします。

※2 Freedom E SDKとは、SiFiveが提供するベアメタル開発用のSDKです。Freedom Studioを使うことで、Freedom E SDKを活用した開発がとても簡単に行えます。

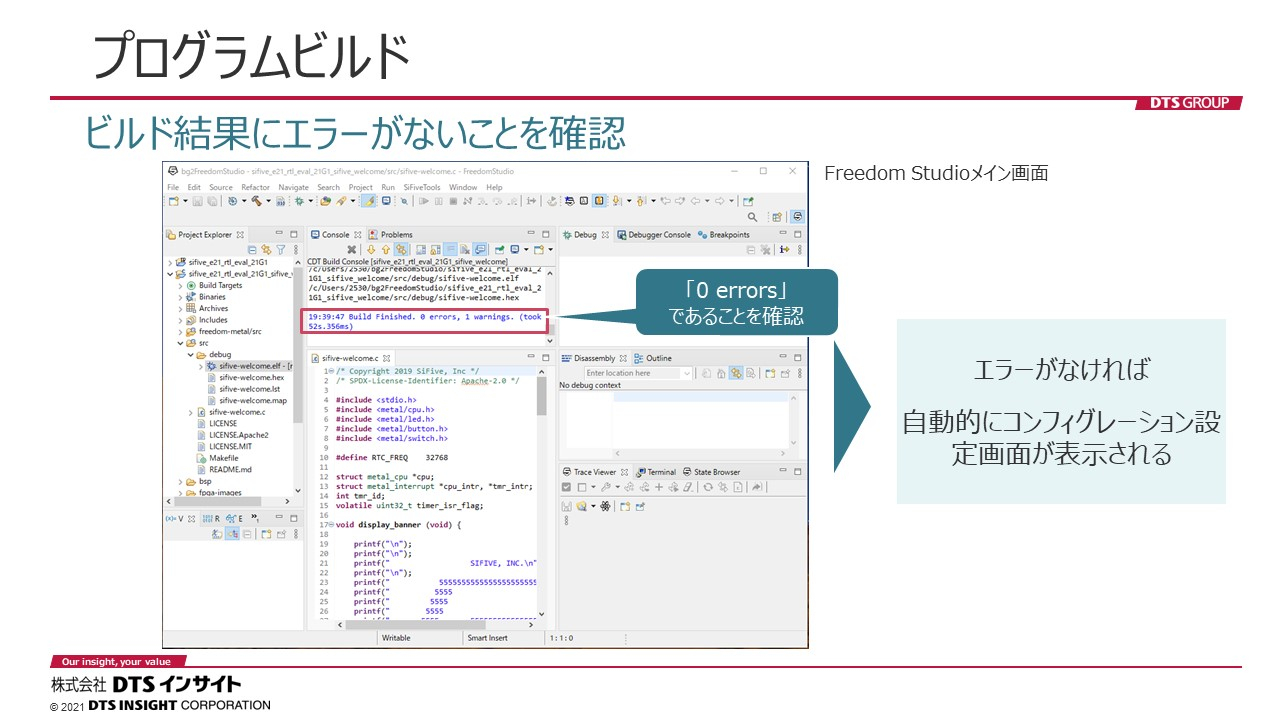

4.プログラムビルド

前章の最後で行った”Finish”ボタンのクリックにより、自動的にビルド(Cソースプログラムのコンパイル)が開始されます。今回は、デバッグ操作を行うために必要な情報が付加されたプログラムを作るためのビルド(Debugビルド)を行っています。下図の様に、Debugビルド結果にエラーがないことを確認します。

エラーがなければ自動的にコンフィグレーション設定画面が表示されます。

5.Debug実行

本章では、出来上がったプログラムをFPGAに実装されたRISC-V Core上にダウンロードし、デバッグ操作を行う様子をご紹介します。

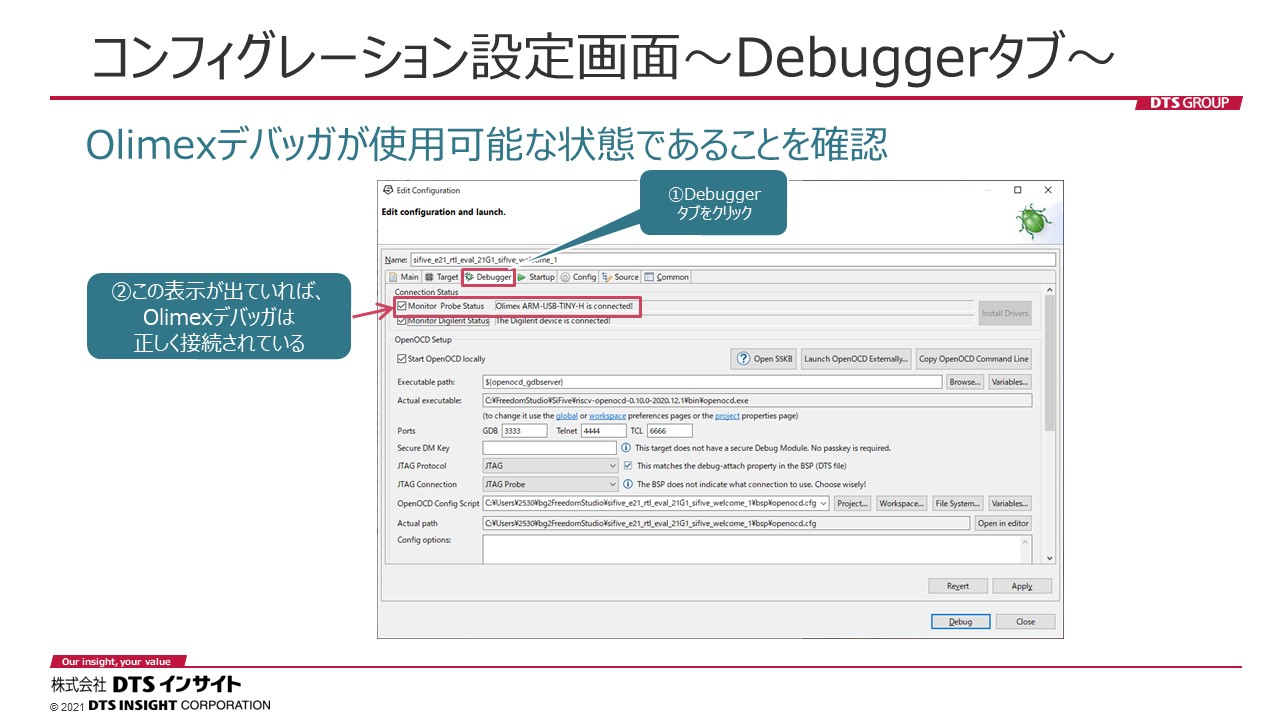

(a)コンフィグレーション設定画面

まず、コンフィグレーション設定画面にて、Olimexデバッガが正しく接続され、使用可能な状態であることを確認します。

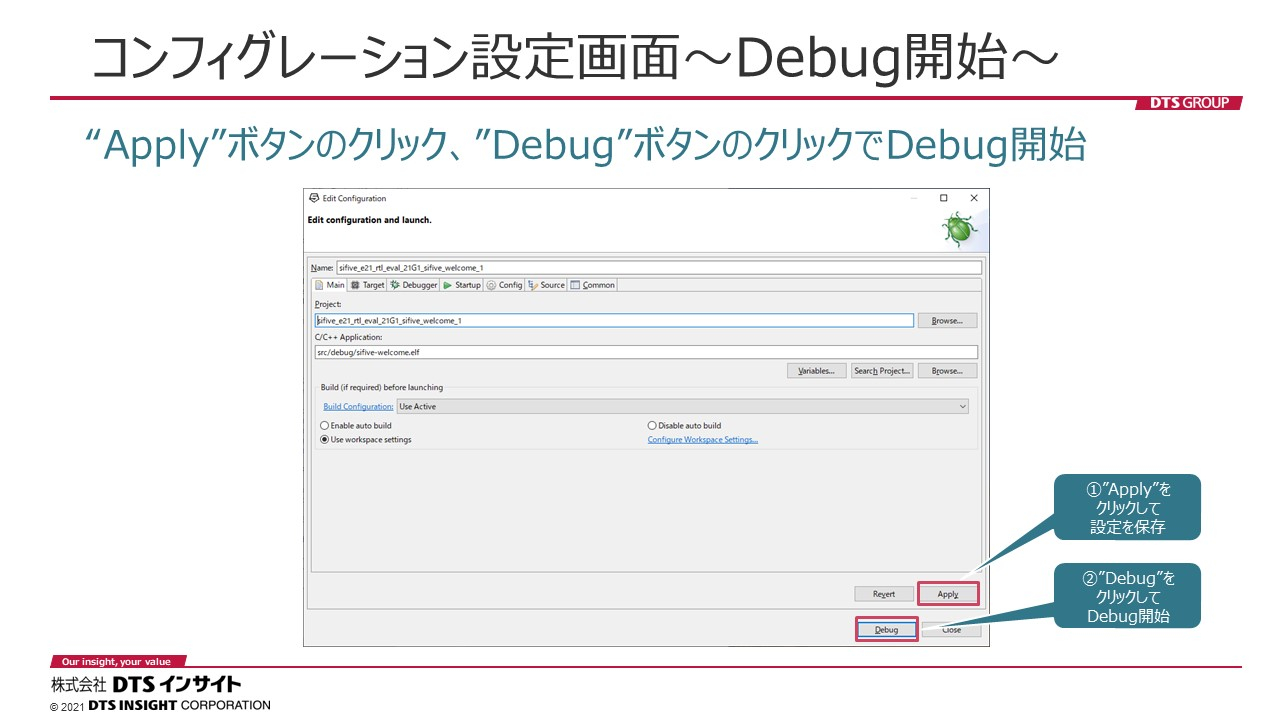

(b)Debug開始

コンフィグレーション設定画面での設定内容は特に変更せずに、デフォルト設定のままDebugを開始します。

下図のコンフィグレーション設定画面で”Apply”ボタンをクリック、次に”Debug”ボタンをクリックすることで、今回作成したプログラムがFPGAボードにダウンロードされます。ダウンロードされたプログラムは自動的に実行が開始されます。

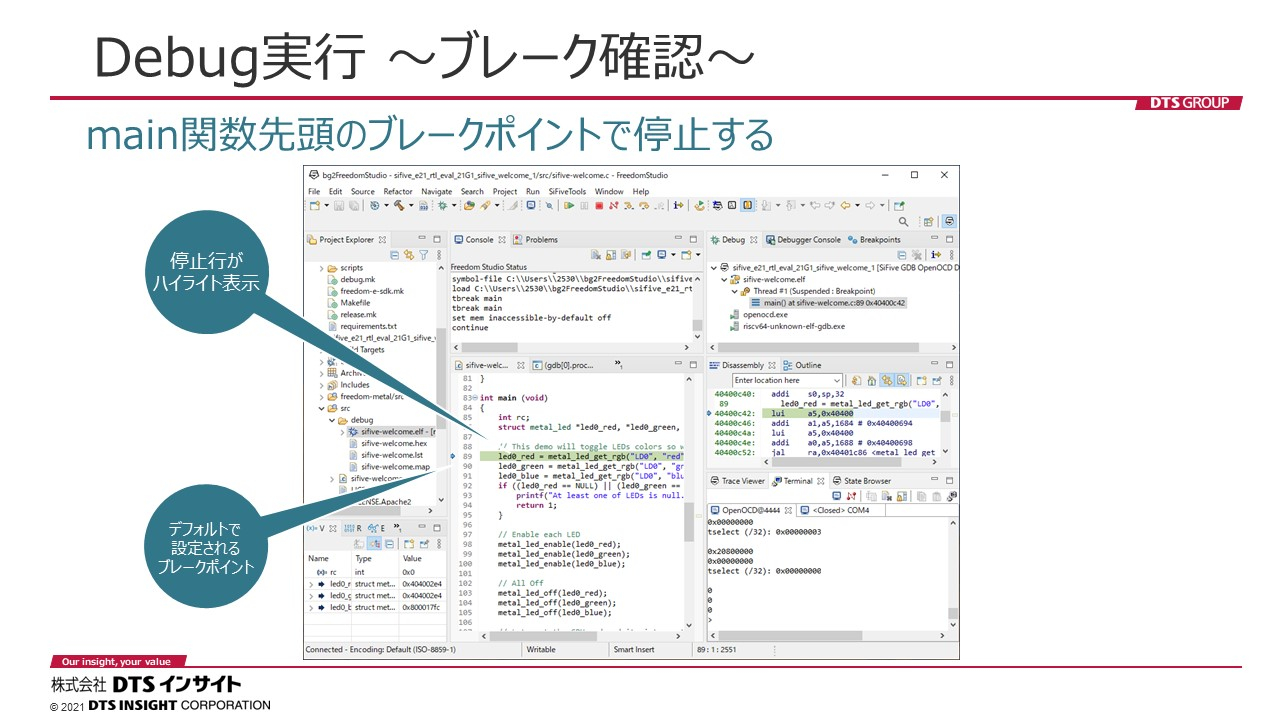

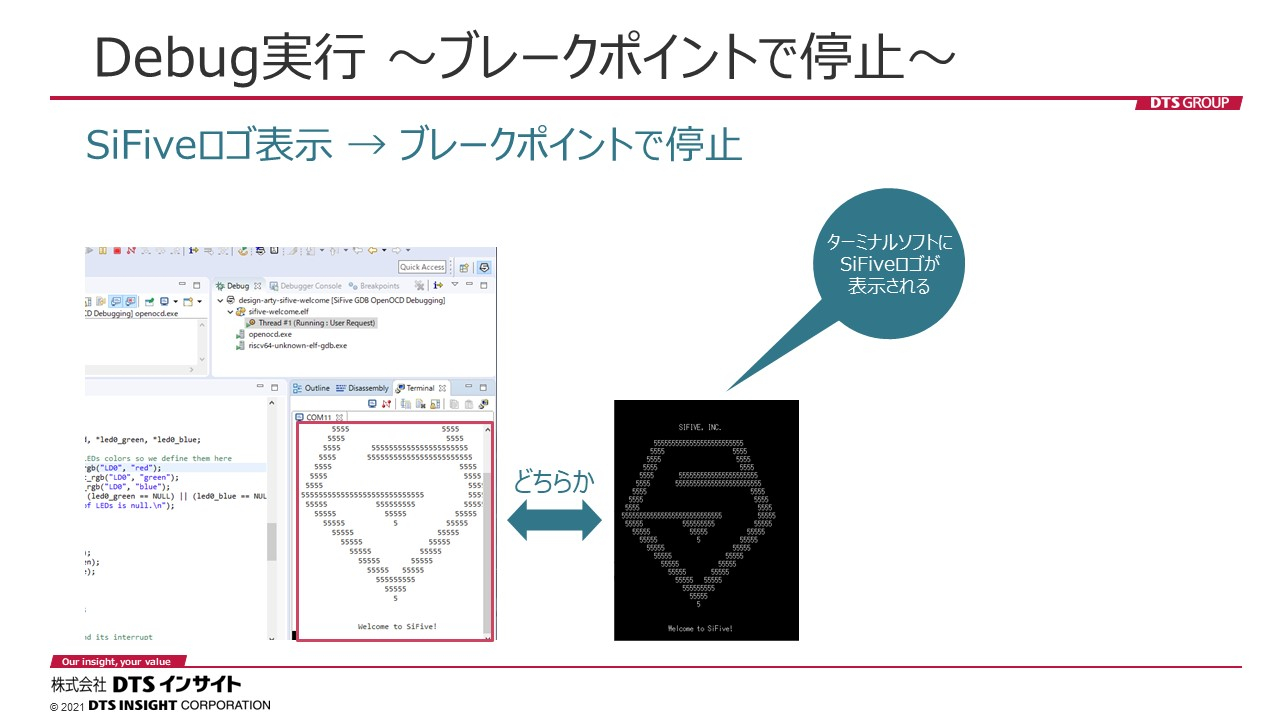

(c)ブレーク確認

プログラムが正常に実行開始されると、すぐにmain関数の先頭で停止します。これはコンフィグレーション設定画面におけるデフォルト設定で、main関数の先頭にブレークポイントを設定しているためです。

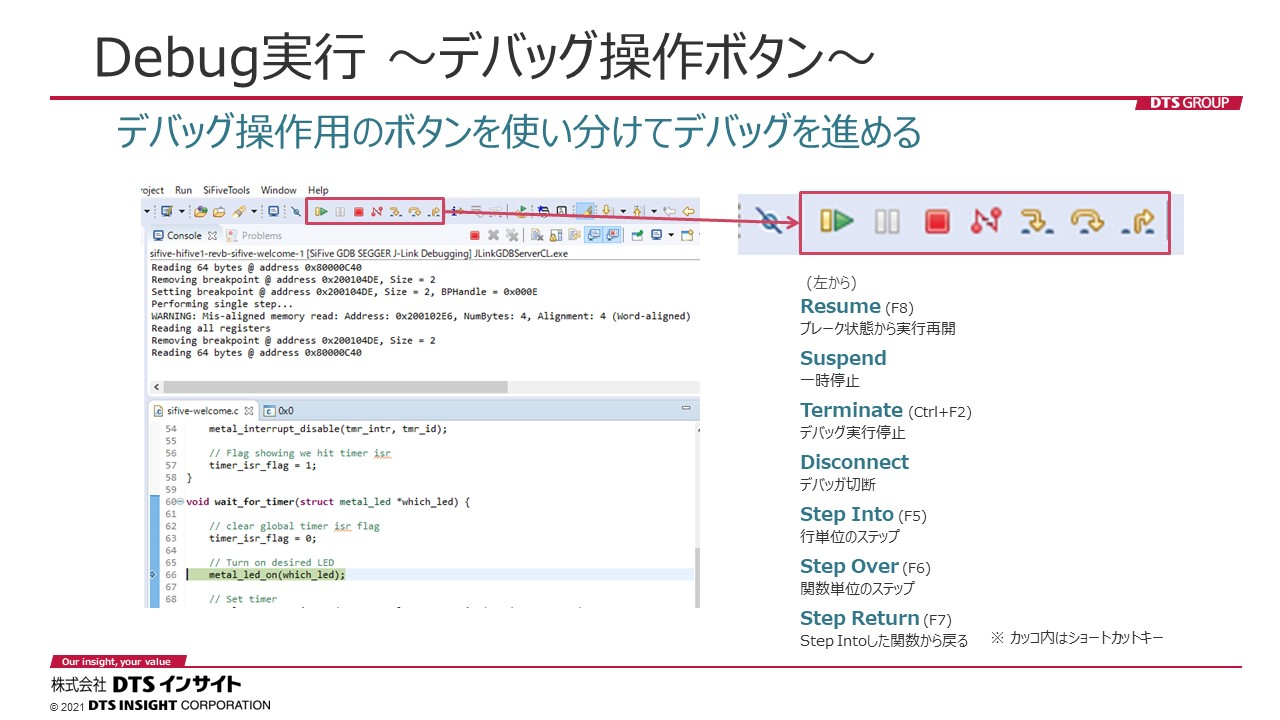

(d)デバッグ操作

Freedom Studioは、下図のようなデバッグ操作用のボタンが用意されており、一般的なデバッガと同様の操作を行うことができます。

“Step Over”ボタンを3回ほどクリックしてFreedom Studio上でソースコード表示View、Disassembly View及びその他のViewの表示が変更される様子を確認します。

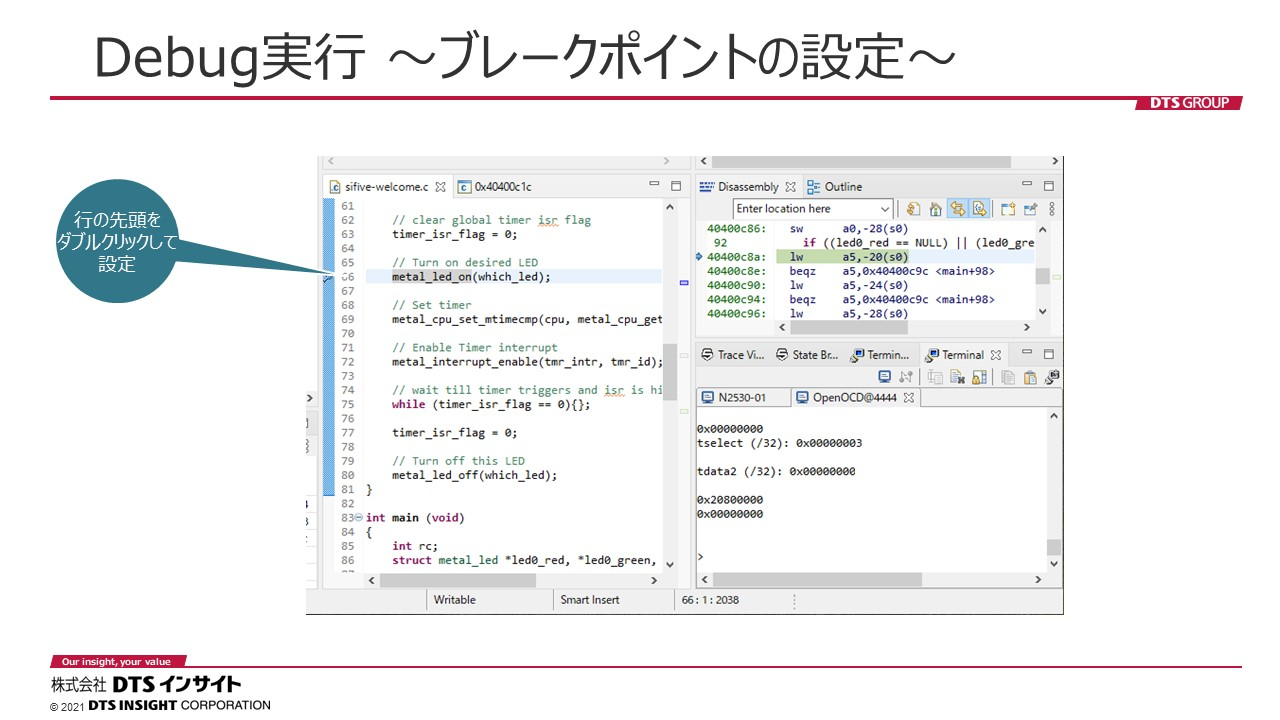

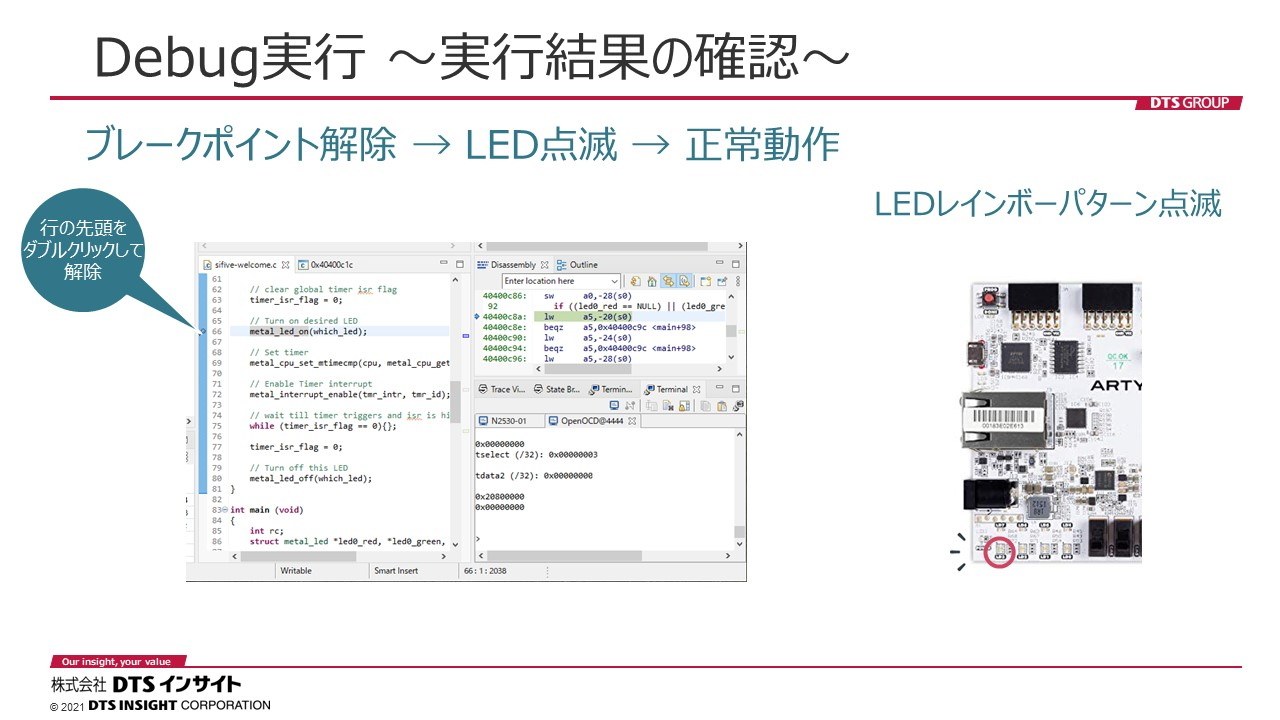

次に、ソースコード表示Viewて、66行目のコードにブレークポイントを設定します。

行の先頭位置をダブルクリックすることで、ブレークポイントを設定します。

“Resume”ボタンをクリックすると、ターミナルソフトには以下の図の様に、SiFiveのロゴが出力され、先程設定したブレークポイントの位置で停止します。

ここで”Step Over”ボタンをクリックすると、metal_led_on()関数が実行されることによって、LEDが赤く点灯します。

(e)実行結果の確認

最後にブレークポイントの設定を解除して”Resume”ボタンをクリックすると、ブレークすることなく実行され、LEDがレインボーパターン(赤→緑→青→赤…)で点滅を繰り返します。

6.まとめ

今回は、Freedom Studioを使って、FPGAボードに実装されたRISC-V Core上でのプログラムの実行やデバッグについてご紹介してきましたが、いかがでしたでしょうか。SiFive RISC-V Coreを簡単にご評価いただけることがおわかりいただけたのではないかと思います。

ほんのさわりのご紹介でしたが、Freedom Studioには様々なデバッグ機能が用意されています。詳しくはこちら(https://www.sifive.com/software)にあります、ユーザーマニュアルをご覧ください。

今回のブログでは触れておりませんが、実はSiFive RISC-V Coreは、ブラウザ上で簡単かつ自由にCore構成をカスタマイズすることができる、SiFive Core Designerというツールが用意されています。たとえば、RISC-Vをマルチコア構成にしてご評価いただく、といったことがこのツールを使うことでとても簡単に実現できます。

SiFive Core Designerにつきましてご興味ございましたら、ぜひ当社までご連絡ください。

次回は、いよいよ出荷が開始されましたHiFive Unmatchedボードに関する最新情報をお伝えする予定です。

お楽しみに!

■■DTSインサイトの「システムLSI設計ソリューションサービス」■■

DTSインサイトでは、システムLSI/FPGA設計の受託も行っています。

当社のノウハウを活かした、ソフトウェアの移行(マイグレーション)

サービスも提供しておりますので、お気軽にご相談ください。

システムLSI設計ソリューションサービス紹介は こちら