1.はじめに

前回、RISC-V技術ブログ連載第11回「SiFive最新リリース HiFive Unmatchedボードのご紹介⑦ 」では、 「HiFive Unmatched でベアメタルプログラミングに挑戦(前編)」と題して、 LinuxなどのOSを用いずに動かすプログラムの作成、動作を行うための事前準備についてお伝えしました。

今回は「 HiFive Unmatched でベアメタルプログラミングに挑戦(後編) 」と題して、残りの事前準備を行った後、ベアメタルプログラミングのサンプルプログラムのダウンロード、そしていよいよJTAGデバッグに挑戦する様子をお伝えしていきます。

2.サンプルプログラムの配置先を変更する

Freedom Studioを起動し、Freedom E SDK(FESDK)サンプルプロジェクト(sifive-welcome)を作成、ビルドが完了するところまでを前回のブログでお伝えしました。すでに実行可能なファイル(sifive-welcome.elf)ができあがっていますが、初期状態では0x2000 0000(QSPI-Flash)に配置されるようになっています。今回はこれを0x8400 0000(DDR SDRAM)に配置されるように変更します。

2.1.metal.ddr.ldsファイルの作成

まず、sifive-welcomeプロジェクト配下のbsp/metal.default.ldsをコピーして、metal.ddr.ldsファイルを作成後、以下に示すようにRAMの開始アドレス、レングスを変更します。

@@ -12,7 +12,7 @@

MEMORY

{

lim (airwx) : ORIGIN = 0x8000000, LENGTH = 0x1e0000

- ram (airwx) : ORIGIN = 0x8000000, LENGTH = 0x1e0000

+ ram (arw!xi) : ORIGIN = 0x84000000, LENGTH = 0x10000000

rom (irx!wa) : ORIGIN = 0x20000000, LENGTH = 0x10000000

}また、以下のように”rom”と指定されている箇所をすべて”ram”とします。

@@ -103,17 +103,17 @@

KEEP (*(.text.metal.init.*))

KEEP (*(SORT_NONE(.init)))

KEEP (*(.text.libgloss.start))

- } >rom :rom

+ } >ram :rom

.fini : {

KEEP (*(SORT_NONE(.fini)))

- } >rom :rom

+ } >ram :rom2.2.Makefileの変更

次に、metal.ddr.ldsを使うようにMakefileを変更します。テキストエディタでMakefileを開き、以下のように”LINK_TARGET = default”をコメントアウト、”LINK_TARGET = ddr”を追記します。

ifeq ($(LINK_TARGET),)

#LINK_TARGET = default

LINK_TARGET = ddr

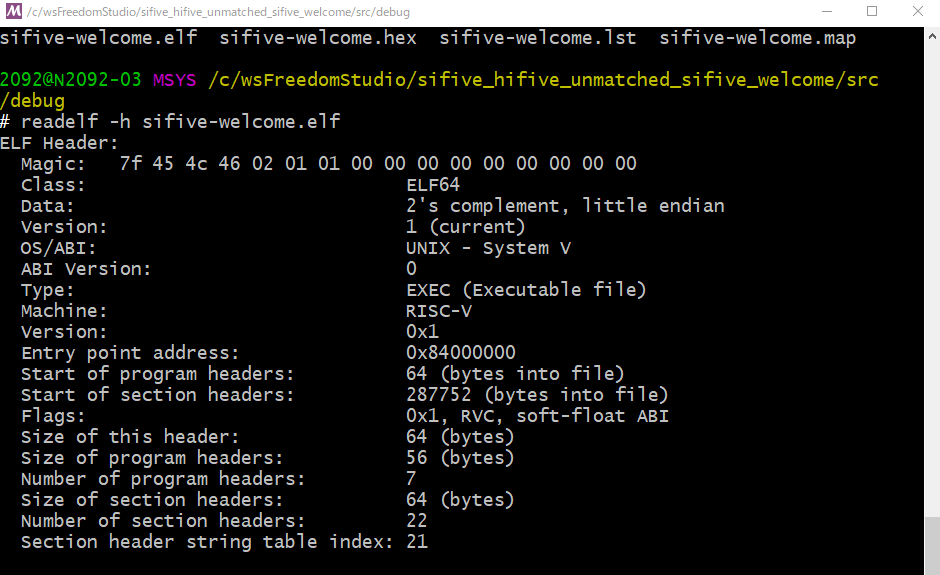

endifこれでビルドの準備が整いました。プロジェクトのクリーン、ビルドを行い、再び sifive-welcome.elf を作成します。念のため、Freedom Studio同梱のmsys2でreadelfを実行し、配置先が変更されていることを確認します。

3.ブレークポイントの設定

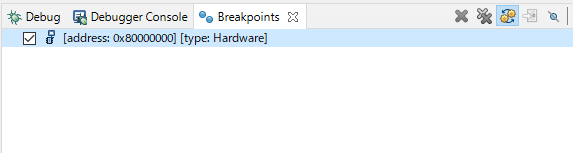

現時点では、sifive-welcomeにDDR SDRAMの初期化処理は含まれていません。そこで、DDR SDRAMを初期化するためにFreedom U SDK(FUSDK)を利用します。FUSDKに含まれるU-Bootが起動する直前でブレークさせることで、DDR SDRAMが初期化され、かつM-Mode(machine Mode)の状態となり、sifive-welcome.elfをダウンロード、実行できます。以下のように、0x8000 0000にハードウェアブレークポイントを設定します。

4.デバッグの開始

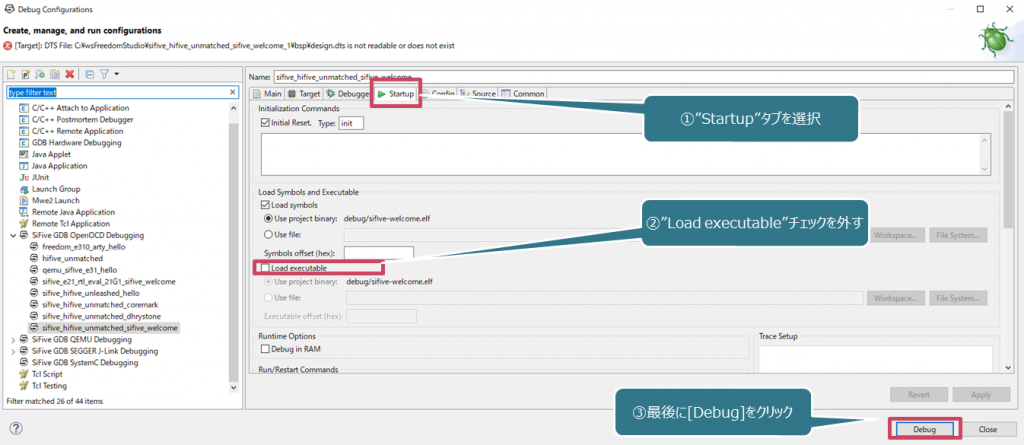

Freedom Studioを使ってデバッグを行う際、初期状態ではデバッグの開始と合わせてelfファイルのダウンロードが行われます。今回、DDR SDRAM初期化後にelfファイルをダウンロードする必要があるため、そのようにデバッグコンフィグレーション設定を変更後、[Debug]ボタンを押してデバッグを開始します。

5.JTAGデバッグ操作

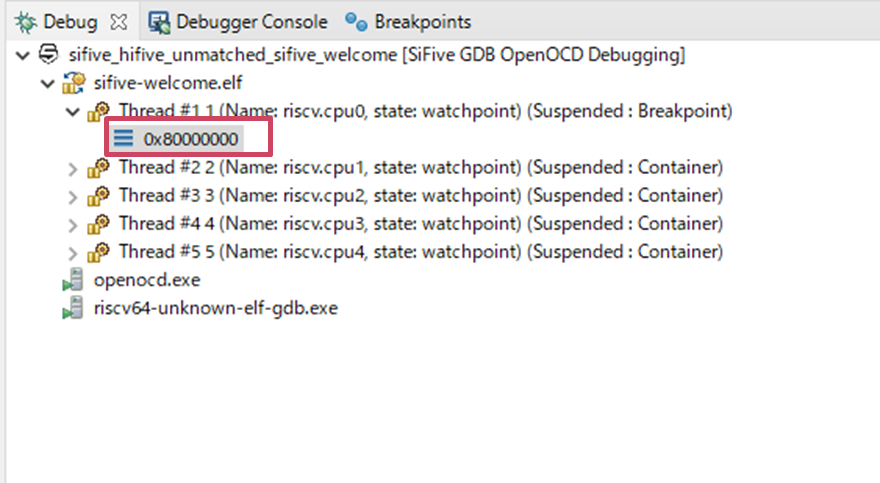

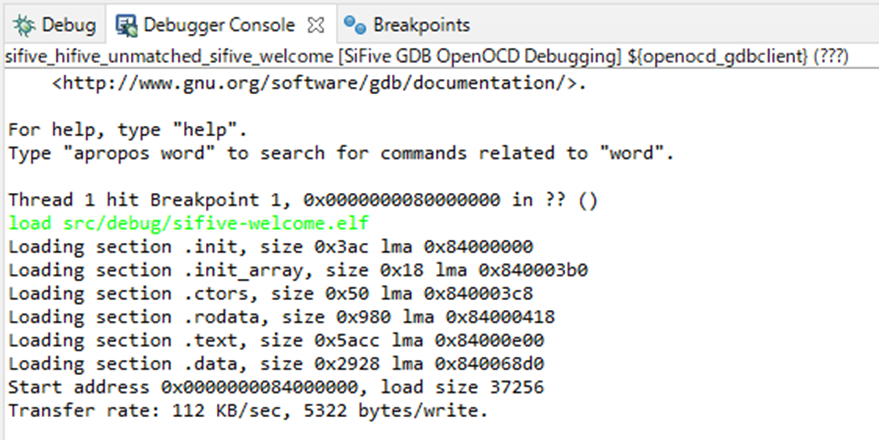

HiFive Unmatchedボードとデバッグ接続が行われた後、しばらく待つと以下のようにU-Bootの先頭アドレス(0x8000 0000)でブレークしました。

ここで、以下のようにloadコマンドを使ってsifive-welcome.elfをダウンロードします。

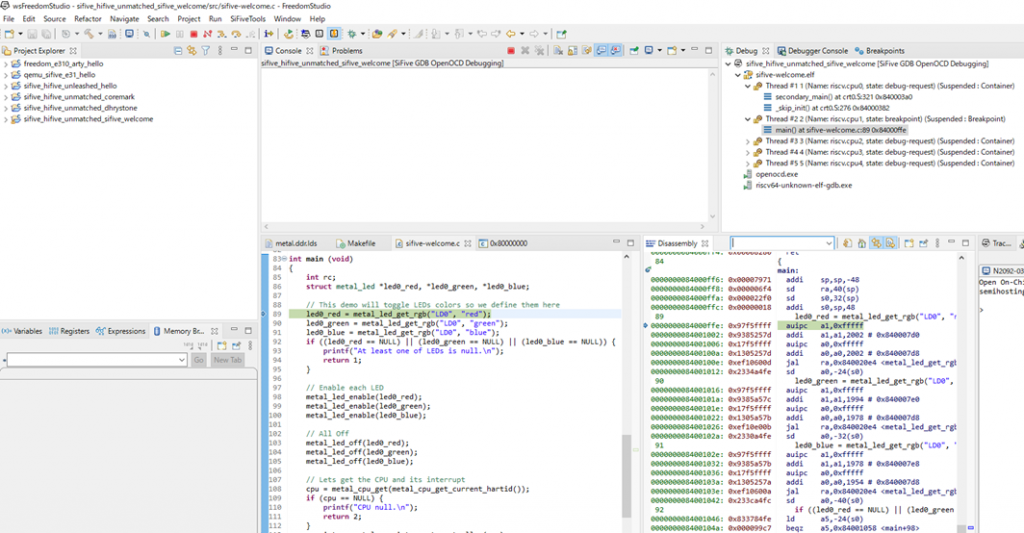

無事ダウンロードできたので、以下のgdbコマンドでプログラムカウンター(PC)をsifive-welcomeの先頭アドレス(0x8400 0000)に設定後、[Resume]ボタンを押して継続実行させます。

thread apply all set $pc=0x84000000すると、すぐにmain()の先頭でブレークしました!

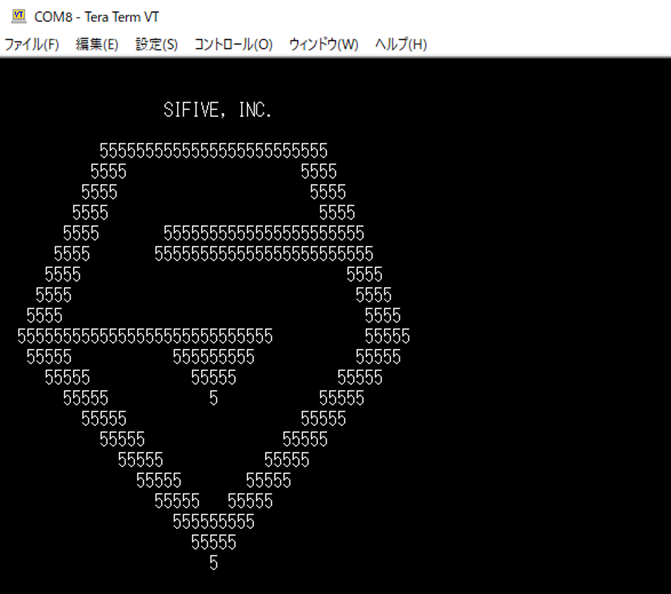

ここで、”Move to Line”により次に実行する行を121行目に設定した後、再び[Resume]ボタンを押します。すると、ターミナルソフトの画面には以下のように期待したSiFiveロゴが出力されました。

6.まとめ

いかがでしたでしょうか。前編、後編の2回に渡ってHiFive Unmatchedボードでベアメタルプログラミングに挑戦する様子をお伝えしてまいりました。今回はあくまでFESDK付属のサンプルプログラムを用いたものでしたが、実際にプログラミングを進める上ではこのようなサンプルプログラムを参考に、Freedom Studioを使って独自の実装とデバッグを進めることになります。

なお、今回ご紹介した内容は、先日開催されましたRISC-V Days Tokyo 2021 AutumnにおけるオンラインRISC-Vパビリオン内で、デモ動画「HiFive Unmatchedボード JTAGデバッグに挑戦」として公開していました。現在も引き続き公開中ですので、ぜひこちらよりお立ち寄りください。

次回も引き続きHiFive Unmatchedボードの話題をお伝えしたいと思っています。どうぞお楽しみに!

本ブログについてのより詳しい内容へのご質問等ございましたら、ぜひお気軽にお問合せください。

お問い合わせはこちら

info-lsi@dts-insight.co.jp

■■DTSインサイトの「システムLSI設計ソリューションサービス」■■

DTSインサイトでは、システムLSI/FPGA設計の受託も行っています。

当社のノウハウを活かした、ソフトウェアの移行(マイグレーション)

サービスも提供しておりますので、お気軽にご相談ください。

システムLSI設計ソリューションサービス紹介は こちら