1.はじめに

今回のブログは、RISC-VのISA(Instruction Set Architecture)に関するもので、最近リリースされた内容(拡張命令と基本命令の一部)をご紹介します。RISC-VのISAは、RISC-Vの非営利団体:RISC-V Internationalにて技術的に検討とレビューされた後、Ratified ISAとしてリリースされます(*1)。今回ご紹介するのは、昨年11月にRatifiedされて発表されたものです(以下のURL参照)。

https://riscv.org/announcements/2021/12/riscv-ratifies-15-new-specifications/

*1

RISC-V Internationalでの仕様検討とレビューは、次に示す段階(上から下へ)を踏みます。

・Discussion Document : 議論の対象の段階。全ての記述は変更可能。

・Development : 開発段階。全ての記述は変更可能。

・Stable : 変更可能であるが限定的。

・Frozen : 基本的に変更なし。Public reviewで重大案件があれば変更。

・Ratified : 最終段階。変更及び改訂不可。

上記の段階を経て、Ratified となり仕様が決定されます。

2.RISC-V ISA 構造について ~おさらい~

ここではRISC-V ISAの基本構造についておさらいをしてみたいと思います。

RISC-V ISA は、「基本命令(Base Instruction) + 拡張命令 (Extension)」というモジュラー構造になっています。今回のリリースもこの基本構造に則って実施されました。

下図に示します様に、RISC-V ISAの基本構造は、4つの基本命令(Base Instruction)であるRV32E、RV32I、RV64I、RV128Iが定義され、これらいずれかの実装が必須となっております。

この基本命令に対して、必要に応じてさまざまな拡張命令(Extension)を追加するというモジュラー構造を取っており、これによりそれぞれの目的とする実装に対して最適な構成をとることが可能となっています。

出典:「SiFive RISC-V紹介記事が電波新聞ハイテクノロジーに掲載されました」https://www.dts-insight.co.jp/topics/index.php?m=TopNote&id=178

3.今回 Ratified された仕様(Extension)の概要

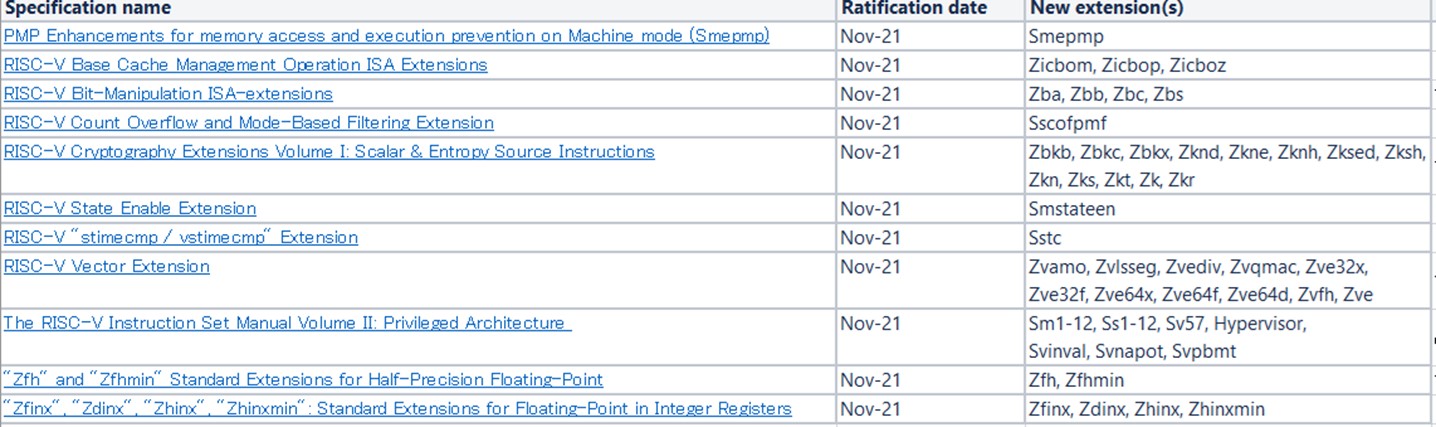

今回Ratifiedされリリースされたものを以下の表に示します。

参照URL:

https://wiki.riscv.org/display/HOME/Recently+Ratified+Extensions

Ratification date:November 2021

11種類のISA(新規拡張命令と既存の命令に対する補完及び拡張)が、2021年11月にRatifiedされてリリースされ、12月に発表されました。11種類の内訳は、PMPの機能向上、Cache管理、ビット処理、Cryptography、Vector、Hypervisor、半精度対応などですが、これらの項目の中で、次の3つが新規で大きな追加となっています。

- Cryptography Extension

- Vector Extension

- Hypervisor (Privileged Architecture)

次に上記3つの項目についてそれぞれ説明します。

3.1.Cryptography Extension

これはセキュリティに関係するCryptographyの拡張命令セットで、今回新規にリリースされました。Cryptographyは暗号化・復号化の手法及びアルゴリズムでスタンダードの規約があります。今回のリリースが対応している規約は、米国系(NIST)のAES、SHA2と、中国系(ShanMi)のSM3,SM4です。

(略号の意味は以下の通り)

NIST : National Institute of Standards and Technology

AES : Advanced Encryption Standard

SHA : Secure Hash Algorithms

SM3 : A cryptographic hash function used in the Chinese National Standard

SM4 : A block cipher algorithm. Standardization Administration of China

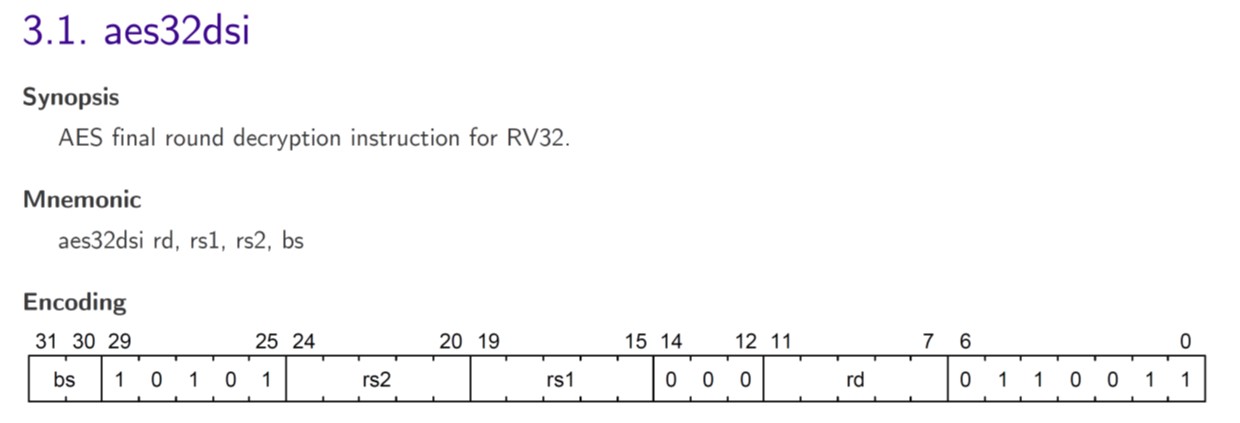

Cryptography ISAの一例として、新たに追加されたaes32dsi 命令をご紹介します。

aes32dsi 命令については、Cryptography ISAの仕様にて以下の様に定義されています。これは、AESの復号化の処理の中で実行されるものです。

出典:以下のURLで参照のPDF中の Page 10

https://github.com/riscv/riscv-crypto/releases/download/v1.0.0-scalar/riscv-crypto-spec-scalar-v1.0.0.pdf

なお、SiFiveでは、Cryptography Extensionを実装するHW IPを開発中です。

参照URL:RISC-V Cryptography extension について

https://github.com/riscv/riscv-crypto/releases/tag/v1.0.0-scalar

3.2.Vector Extension

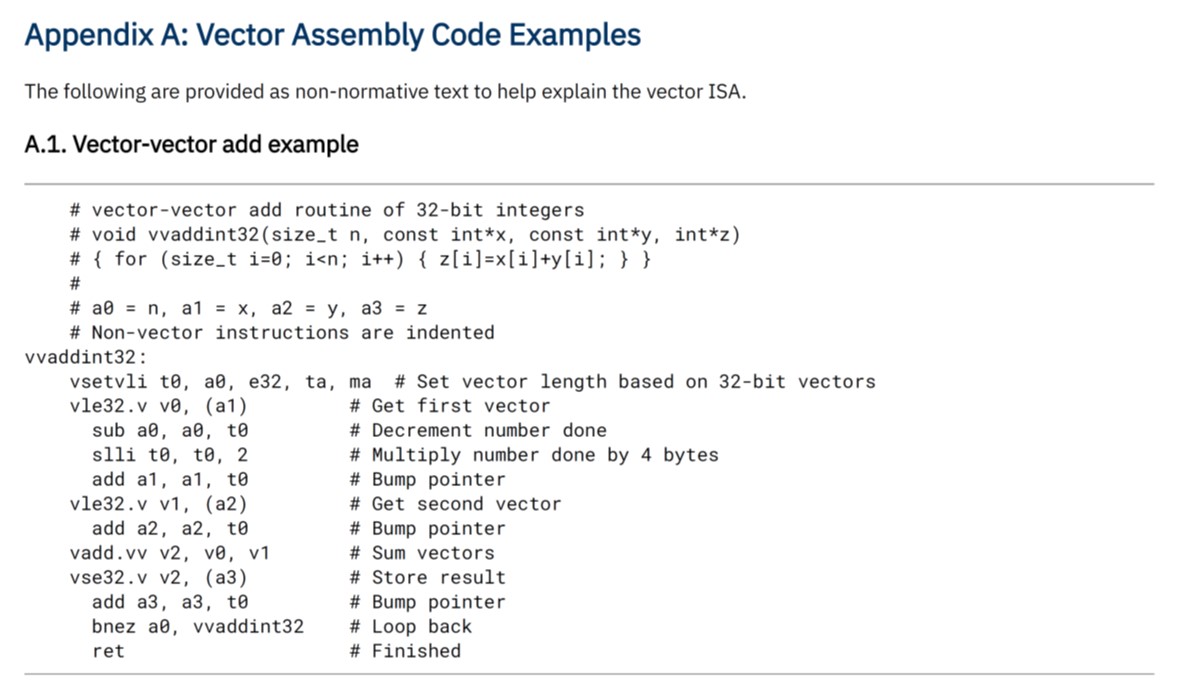

これはVector演算を実行するためのISAで、Vector演算実行用のHWを備えていると能力を発揮します。Vector用レジスタの設定や、Vector演算のビット幅の定義も含まれていてHWとの連携が必要です。

アセンブラでのサンプルコードを以下に示します。この例はVector間の加算をプログラムしたものです。

出典:以下のURLで参照のPDF中の Page 99

https://github.com/riscv/riscv-v-spec/releases/download/v1.0/riscv-v-spec-1.0.pdf

なお、SiFiveは Vector Extensionを実装したIPを先行開発し、すでにリリースしています。P270、X280がそれに該当します。

P270、X280については、以下のURLをご参照ください。

- P270

https://www.sifive.com/cores/performance-p270 - X280

https://www.sifive.com/cores/intelligence-x280

参照URL:RISC-V Vector extension について

https://github.com/riscv/riscv-v-spec/releases/tag/v1.0

3.3.Hypervisor (Privileged Architecture)

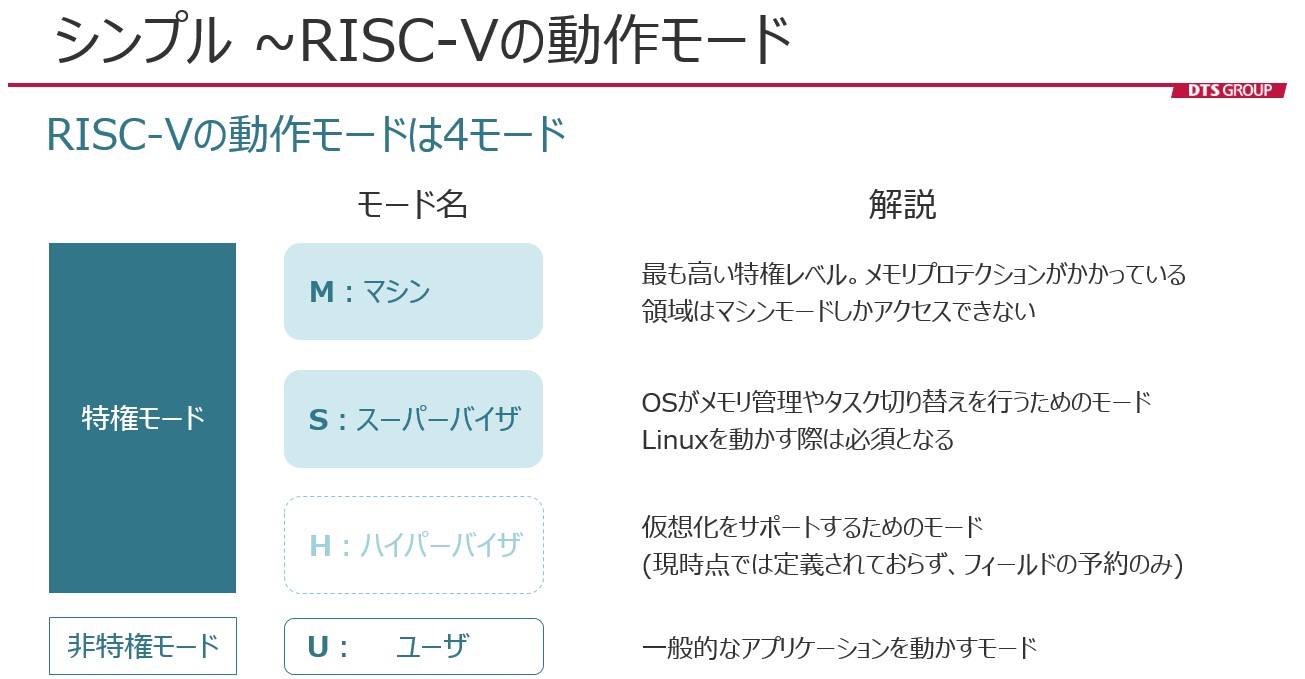

今回のリリース前のRISC-V ISAでは、以下に示す様に 「H:ハイパーバイザ」 が予約されているのみで、未定義な状態でした。

出典: 「SiFive RISC-V紹介記事が電波新聞ハイテクノロジーに掲載されました」https://www.dts-insight.co.jp/topics/index.php?m=TopNote&id=178

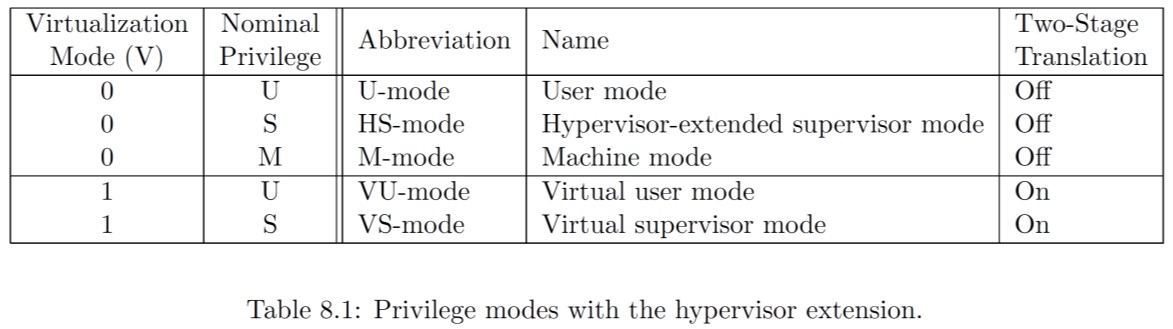

今回のリリースで、上記の「ハイパーバイザ」に対応するものとして、以下の表に示すモードを新たに定義しました。

Version 20211105-signoff”, Editors Andrew Waterman, Krste Asanovi´c, and John Hauser, RISC-V

International, November 2021.

出典:以下のURLで参照のPDF中の Page 98

https://github.com/riscv/riscv-isa-manual/releases/download/draft-20211105-c30284b/riscv-privileged.pdf

いちばんのポイントとなるのは、仮想化を実現するために新たなモード:Virtualization Mode を定義したことです。これによりハイパーバイザ拡張が有効なシステムにおいては、従来のU/S/Mの3つの動作モードに対し、新たにU/HS/M及びHS-mode上で動作するVU/VMの合計5つのモードが実装され、追加されたモードの制御に関連するCSR群を定義することで仮想化を実現しています。

なお、SiFiveは Hypervisor を実装したIPを先行開発し、すでにリリースしています。P650がそれに該当します。

P650については、以下のURLをご参照ください。

https://www.sifive.com/cores/performance-p650

参考URL:RISC-V Hypervisor について

https://github.com/riscv/riscv-isa-manual/releases/download/draft-20211105-c30284b/riscv-privileged.pdf

4.まとめ

いかがでしたでしょうか。

RISC-V ISA は、その構造上、拡張命令の追加が可能であり、RISC-V International によって拡張命令の指定や開発が管理・運営されています。既に予約された拡張命令があり、また新規に開発されるものもあります。

RISC-V ISAの、「シンプル」、「拡張性」、「オープン」の特徴を活かしてRISC-Vはインダストリ、民生機器、通信、運輸、データセンターなどの領域を中心として利用が広がっていくと予想されています。

新しい考え方によるISAであり、今後も新規に拡張及び追加が継続していきます。

SiFive社は、RISC-V Internationalと連携し、新しいISAに対応したIPをいち早く開発、リリースしており、今後も継続していきます。

本ブログについてのより詳しい内容へのご質問等ございましたら、ぜひお気軽にお問合せください。

お問い合わせはこちら

info-lsi@dts-insight.co.jp

注:

RISC-V InternationalによってRatifiedされたISA仕様は、クリエイティブ・コモンズ・ライセンス(表示4.0国際)のもとに提供されています。

クリエイティブ・コモンズ・ライセンス(表示4.0国際)

https://creativecommons.org/licenses/by/4.0/deed.ja

■■DTSインサイトの「システムLSI設計ソリューションサービス」■■

DTSインサイトでは、システムLSI/FPGA設計の受託も行っています。

当社のノウハウを活かした、ソフトウェアの移行(マイグレーション)

サービスも提供しておりますので、お気軽にご相談ください。

システムLSI設計ソリューションサービス紹介は こちら