1. はじめに

今回の技術ブログでは、2022年6月21日にRISC-V InternationalによってRatifiedされたことが発表された(※1)、2022年の最初の4つの仕様と拡張について概要をご説明します。

2. 今回 Ratifiedされた仕様の概要

RISC-Vの非営利団体:RISC-V Internationalでは、ISA仕様はもちろんのこと、RISC-Vのエコシステムを拡充するためのハードウェアおよびソフトウェアの仕様(非ISA仕様)を策定しています。これらはISAと同様に、RISC-V International内で技術的に検討、レビューされた後、Ratified Specificationとしてリリースされます(※2)。

今回Ratifiedされ、リリースされた4件の仕様を以下の表に示します 。

| 仕様 | 概要 | RISC-V Group |

| E-Trace(*1) for RISC-V | 小規模な組込みシステムから大規模なコンピュータまで、あらゆるタイプのアプリケーションのデバッグに役立つ、分岐トレースを使用した効率的なプロセッサトレースのアプローチを定義する。 | SOC Infrastructure Horizontal Committee |

| RISC-V specification for SBI(*2) | スーパーバイザーモード(S-modeまたはVS-mode)のアプリケーションバイナリインターフェースを使用して、ハードウェアプラットフォームとオペレーティングシステムカーネルの間にファームウェア層を構築する。 | RISC-V Platform Specification Task Group |

| RISC-V UEFI(*3) Protocols | 既存のUEFI規格をRISC-Vプラットフォームに導入する。 | RISC-V Platform HSC Group |

| RISC-V Zmmul Multiply Only | RISC-V Unprivileged仕様に含まれるもので、乗算は必要だが除算は不要という低コストな実装を可能にする。 | Unprivileged Architecture Task Group |

*1 Efficient Traceの略

*2 Supervisor Binary Interfaceの略

*3 Unified Extensible Firmware Interfaceの略

出典:

https://riscv.org/announcements/2022/06/risc-v-announces-first-new-specifications-of-2022-adding-to-16-ratified-in-2021-risc-v-international/

https://wiki.riscv.org/display/HOME/Specification+Status

今回のリリースでは、非ISA仕様が主体で、表中の上から3件は非ISA仕様、4件目がISA仕様です。

次に、これら4件についてもう少し詳しく説明します。

※2 RISC-V Internationalでの仕様検討とレビューは、次に示す段階(上から下へ)を踏みます。

・Discussion Document : 議論の対象の段階。全ての記述は変更可能。

・Development : 開発段階。全ての記述は変更可能。

・Stable : 変更可能であるが限定的。

・Frozen : 基本的に変更なし。Public reviewで重大案件があれば変更。

・Ratified : 最終段階。変更及び改訂不可。

上記の段階を経て、Ratified となり仕様が決定されます。

2.1. E-Trace for RISC-V

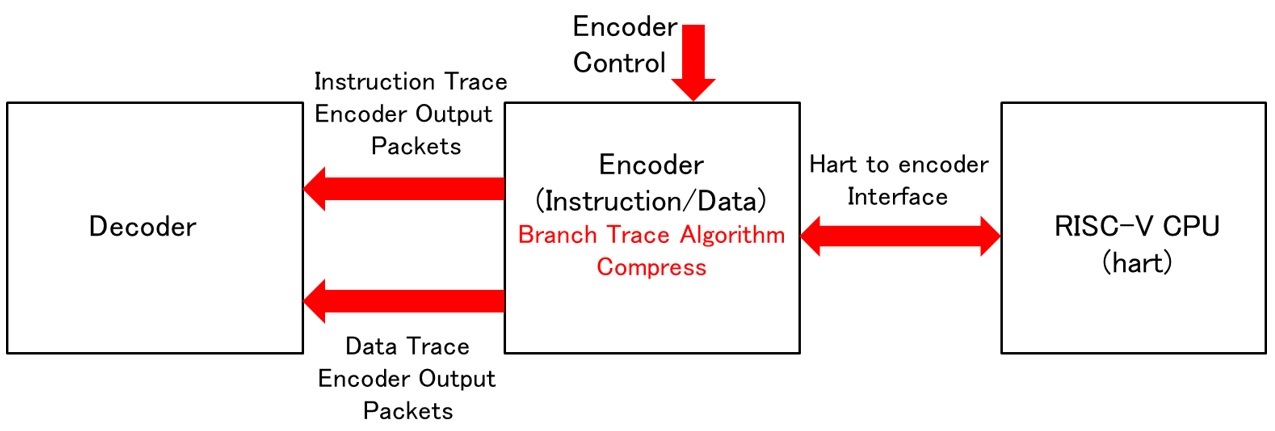

Efficient Trace(以下、E-Trace)は、デバッグ機能の一つであるトレースについて、RISC-Vとして初めてRatifiedされた仕様です。E-Traceは、分岐トレースを採用することによって、フル・トレースと比較して情報量が大幅に削減され、効率的(Efficient)なトレースを実現します。本仕様では、以下の図に示すような関係を説明しています。

RISC-V CPU(hart)でプログラムが実行される際、Encoder Controlにより、hartからEncoderへトレース情報が取り出されます。トレース情報は、Encoder上でBranch Trace Algorithmによって、DecoderにPackets(Instruction/Data)を送るべきか否かを判断します。DecoderがPacketsを受け取る場合、DecoderはPacketsを元のプログラム情報の形にデコードします。本仕様では、これら一連の流れについての詳細が記述されています。

出典:

https://github.com/riscv-non-isa/riscv-trace-spec/blob/main/riscv-trace-spec.pdf

E-Traceが効率的(Efficient)なトレースを実現する上で、Packetsの発行を最小限に留めることが必要です。そこで重要な働きを担うのがBranch Trace Algorithmです。どのようなときにPacketsの発行を抑制できるのか、具体例をご紹介します。

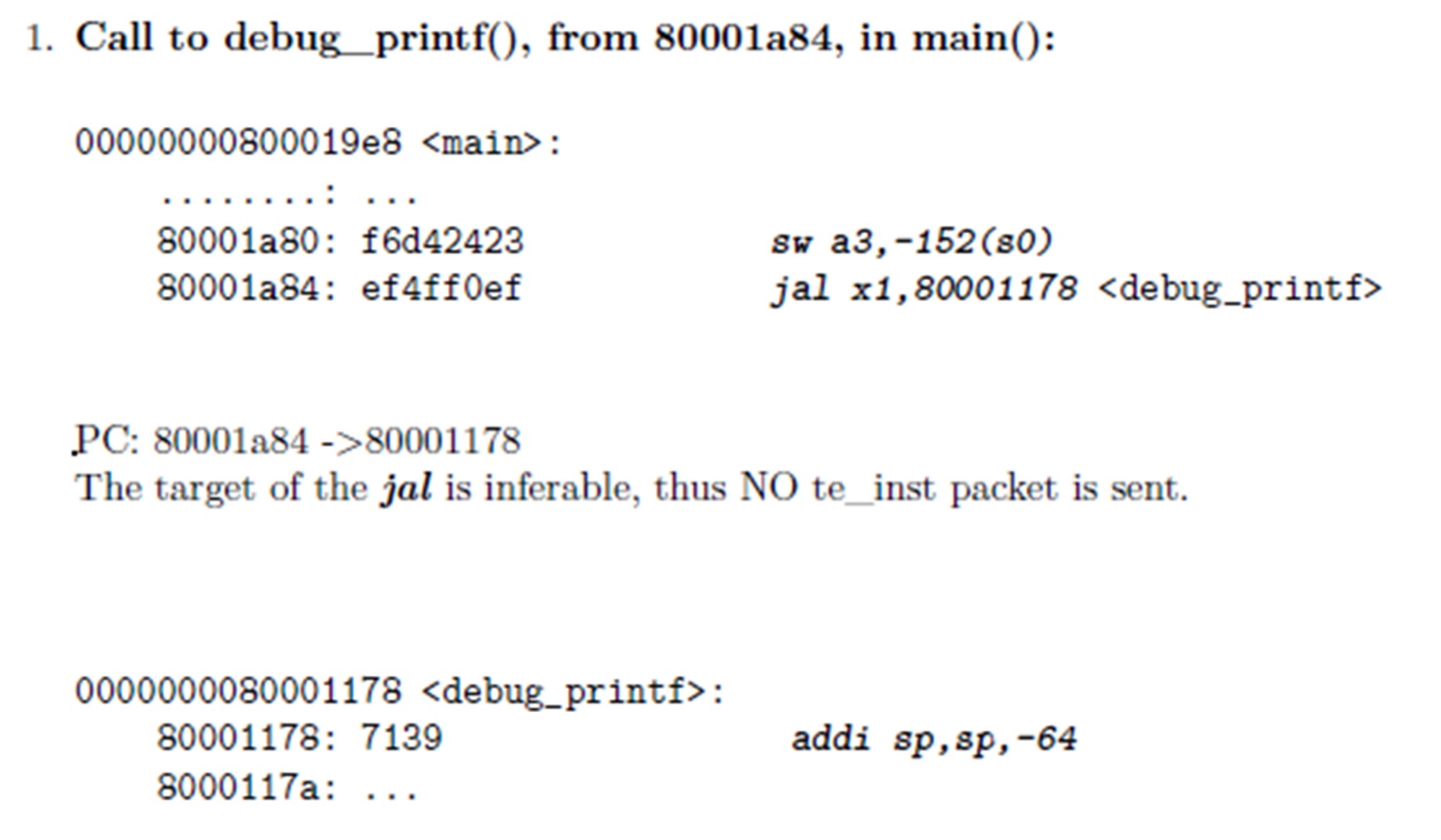

以下のトレース結果は、EncoderからDecoderへPacketsが発行されない例を示しています。

jal (Jump and Link)命令により、debug_printf()に分岐していますが、分岐先のアドレス(0x8000_1178)は事前に特定することが可能です。そのため、te_inst(命令トレースのPackets)は発行されません。

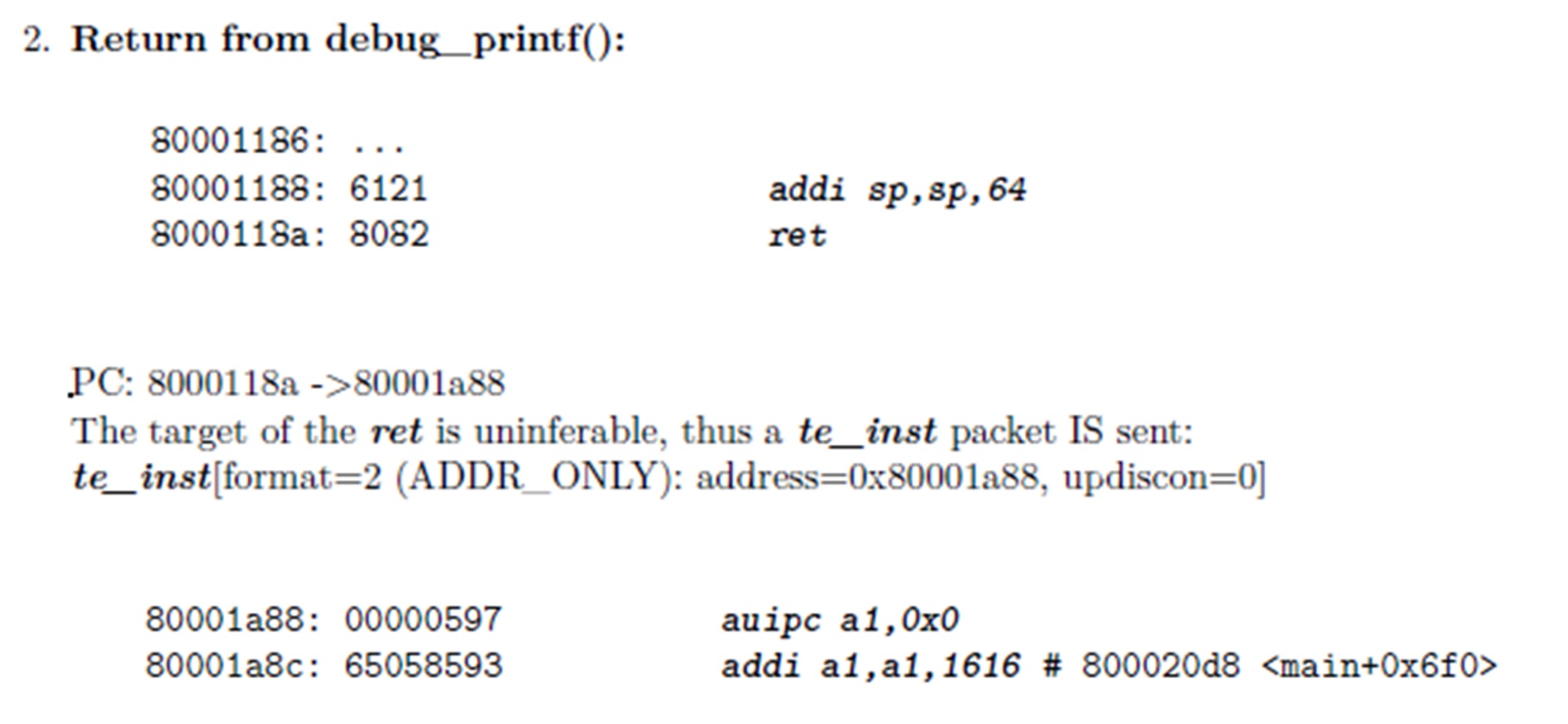

一方、以下に示すトレース結果はEncoderからDecoderへPacketsが発行される例です。

Debug_printf()でのret(リターン)命令は、戻り値を事前に特定することができません。このようなケースではte_instが発行されます。ここでの te_inst の内容は、Format=2 (アドレスのみ、分岐情報なし)で、アドレスには、0x8000_1a88(戻り番地)が指定されます。

このように、Encoder上で動作するBranch Trace Algorithmは、分岐先が特定できるか否かによって、Instruction/DataのPacketsをDecoderに送るべきか否かを判断する役割を担っています。

出典:以下のPDF中の Page 93-94

https://github.com/riscv-non-isa/riscv-trace-spec/blob/main/riscv-trace-spec.pdf

2.2. RISC-V specification for SBI

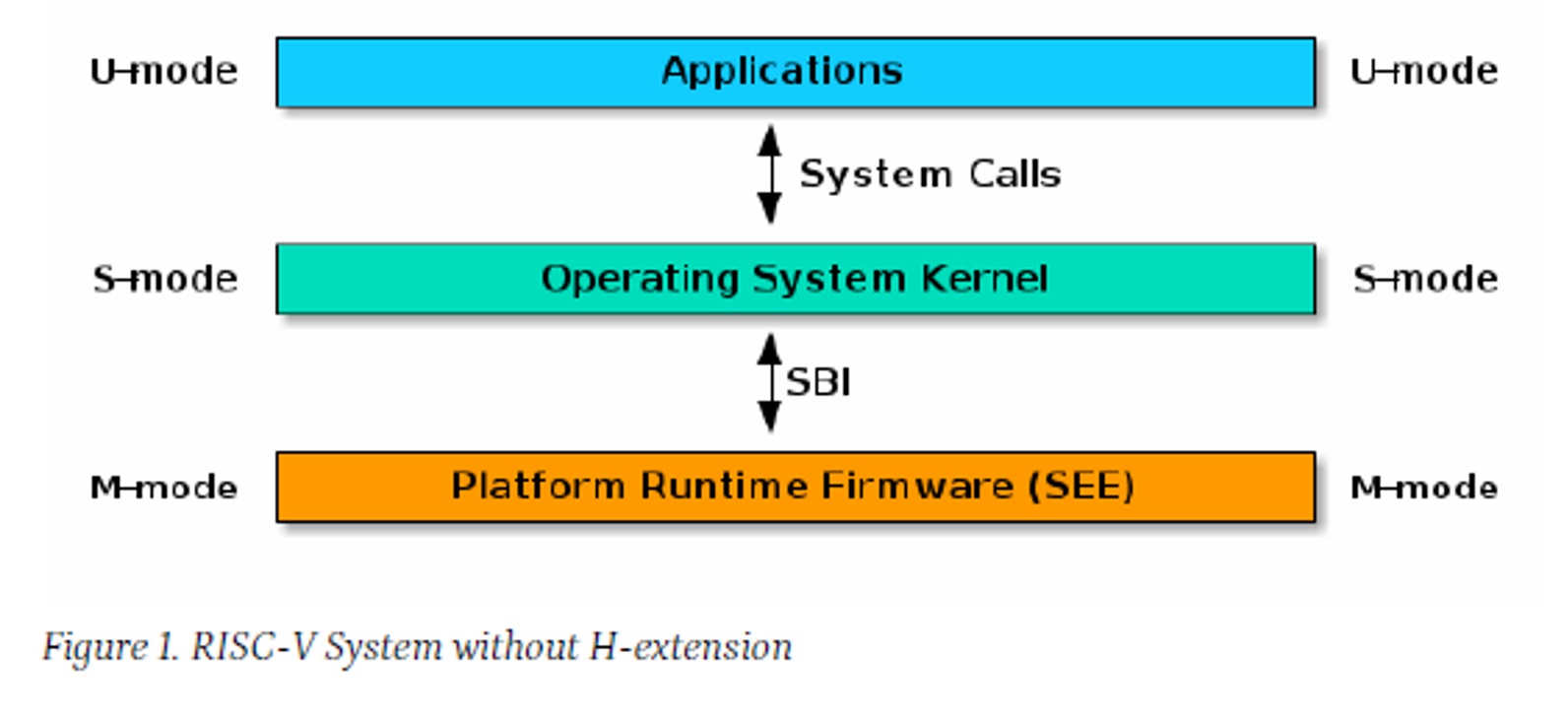

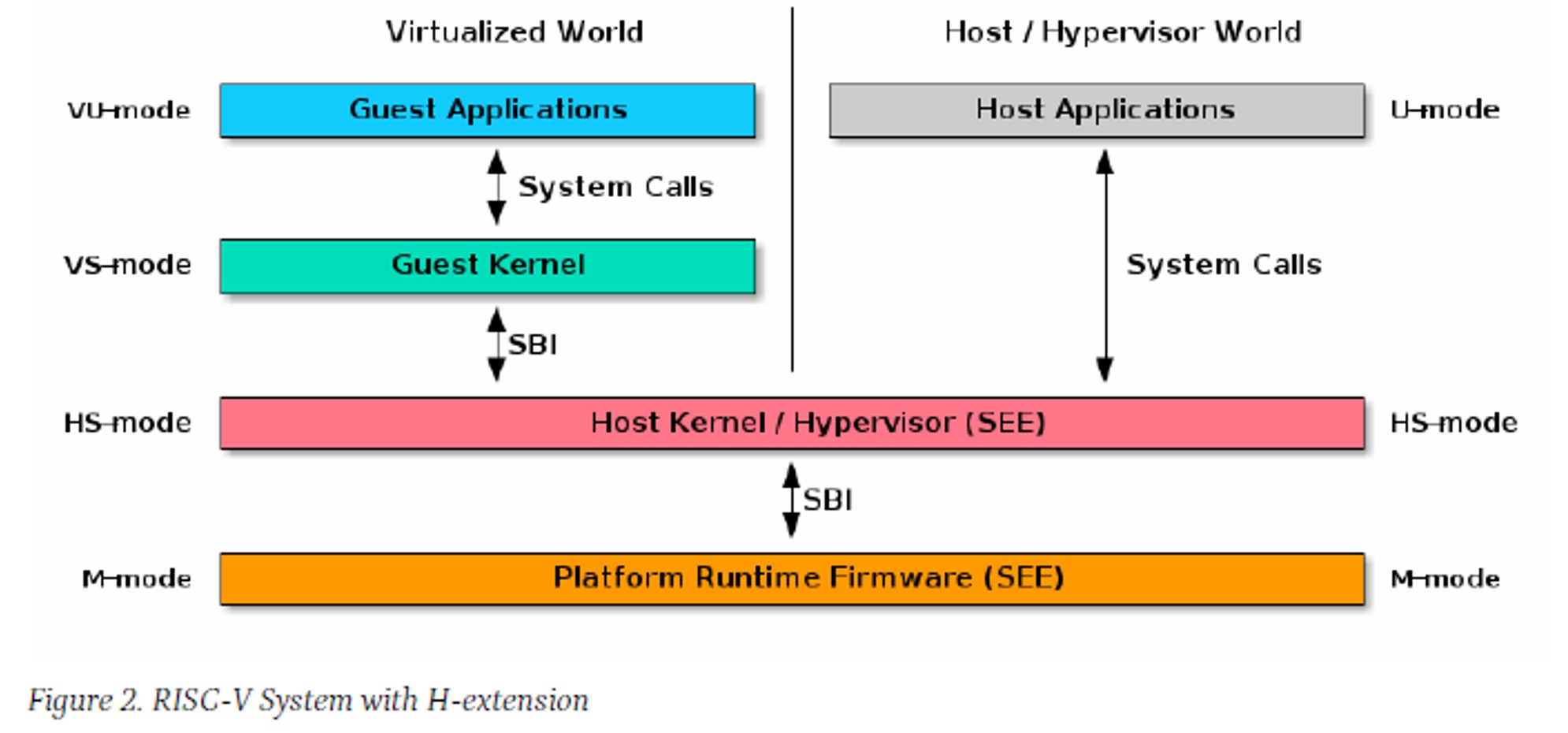

Supervisor Binary Interface (以下、SBI)は、プラットフォーム固有のファームウェア(SEE)と実行中のOS間、さらに仮想化が有効な場合は、ホストOSとゲストOS間でのソフトウェアのインターフェースです。

下図(Figure 1)に示すのは、Hypervisor extensionがない(仮想化が無効)場合でのSBIの適用例です。

下図(Figure 2)は、Hypervisor extensionがある(仮想化が有効)場合でのSBIの適用例です。

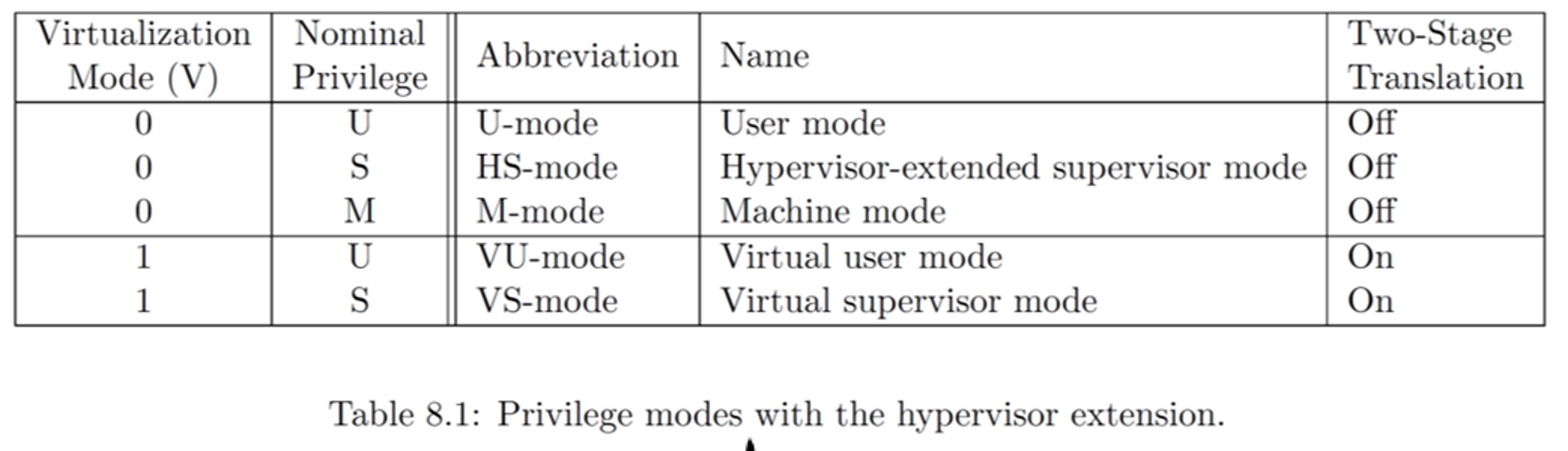

上記の図(Figure 1およびFigure 2)での、各modeは、以前の技術ブログでもご説明したものですが、以下の表を参考にすることができます。

Version 20211105-signoff”, Editors Andrew Waterman, Krste Asanovi´c, and John Hauser, RISC-V

International, November 2021.

出典:

https://github.com/riscv-non-isa/riscv-sbi-doc/releases/download/v1.0.0/riscv-sbi.pdf

https://github.com/riscv/riscv-isa-manual/releases/download/draft-20211105-c30284b/

riscv-privileged.pdf

SBIは、ソフトウェア関数(Function)として定義されており、入力変数、戻り値、エラーコードが規定されていますが、RISC-V ISAにおけるレジスタ、モード、動作等の使用が前提となっています。Functionは、Extensionによって分類が定義されており、どのExtensionに属する、どのFunctionというように指定する形をとります。Extension、FunctionにはそれぞれIDが割り振られており、extension ID(以下、EID)、function ID(以下、FID)で区別されます。

RISC-V では以下のように、それぞれのレジスタに割り当てられます。

・EID — a7 register

・FID — a6 register

・エラーコード — a0 register

・戻り値 — a1 register

SBIの主要なExtensionの内容を、以下の表に示します。

| 名称 | EID | 内容 |

| Base Extension | #0x10 | 最小限の基本的な拡張の内容と、SBI拡張が有効かのプローブ等。 |

| Legacy Extensions | #0x00 – #0x0F | V0.1相当のSBI仕様(※6)。 |

| Timer Extension | #0x54494D45 | Timer 関連。V0.1のSBI仕様から改訂された内容。 |

| IPI Extension | #0x735049 | Inter-processor interrupt 関連。V0.1のSBI仕様から改訂された内容。 |

| RFENCE Extension | #0x52464E43 | Remote Fence 関連。メモリ及びI/Oアクセスの際のread/writeを指示するもので、仮想化の有無両方で定義。V0.1のSBI仕様から改訂された内容 |

| Hart State Management Extension | #0x48534D | Hartの状態を、STOPPED、STARTED、SUSPENDEDの3種類と、4種類のPENDINGとし、状態間の遷移に関するもの |

| System Reset Extension | #0x53525354 | システム・リセットに関するもの。V0.1のSBI仕様から改訂された内容 |

| Performance Monitoring Unit Extension | #0x504D55 | Performance Monitor 関連で、EventのカウントCSR(Control and Status Register)の制御等に関するもの。 |

※6 V0.1のSBI仕様で定義されたFunctionがブートコードの実装に利用された事例があることなどから、V0.1のSBI仕様で定義されたFunctionはLegacy Extensionsとして現在も残されていますが、Legacy Extensionsにしか存在しないFunctionは、今後廃止される可能性があります。

SBIで定義されるFunctionの一例を以下に示します。これは、Base Extension (EID #0x10)の例です。

————————————————-

説明:現行SBI仕様のversionを得る。

EID #0x10

FID #0

struct sbiret sbi_get_spec_version(void);

————————————————-

出典:以下のPDF中の Page 10

https://github.com/riscv-non-isa/riscv-sbi-doc/releases/download/v1.0.0/riscv-sbi.pdf

2.3. RISC-V UEFI Protocols

Unified Extensible Firmware Interface (以下、UEFI) とは、オペレーティングシステム(OS)とファームウェアとの間のソフトウェアインターフェースを定義した仕様です。UEFI自体は、以前から標準仕様が出されており、種々のプラットフォームが対応しています。

UEFIのコンセプトを下図(Figure 1-1)に示します。

出典:以下のPDF中のPage 7

https://uefi.org/sites/default/files/resources/UEFI_Spec_2_9_2021_03_18.pdf

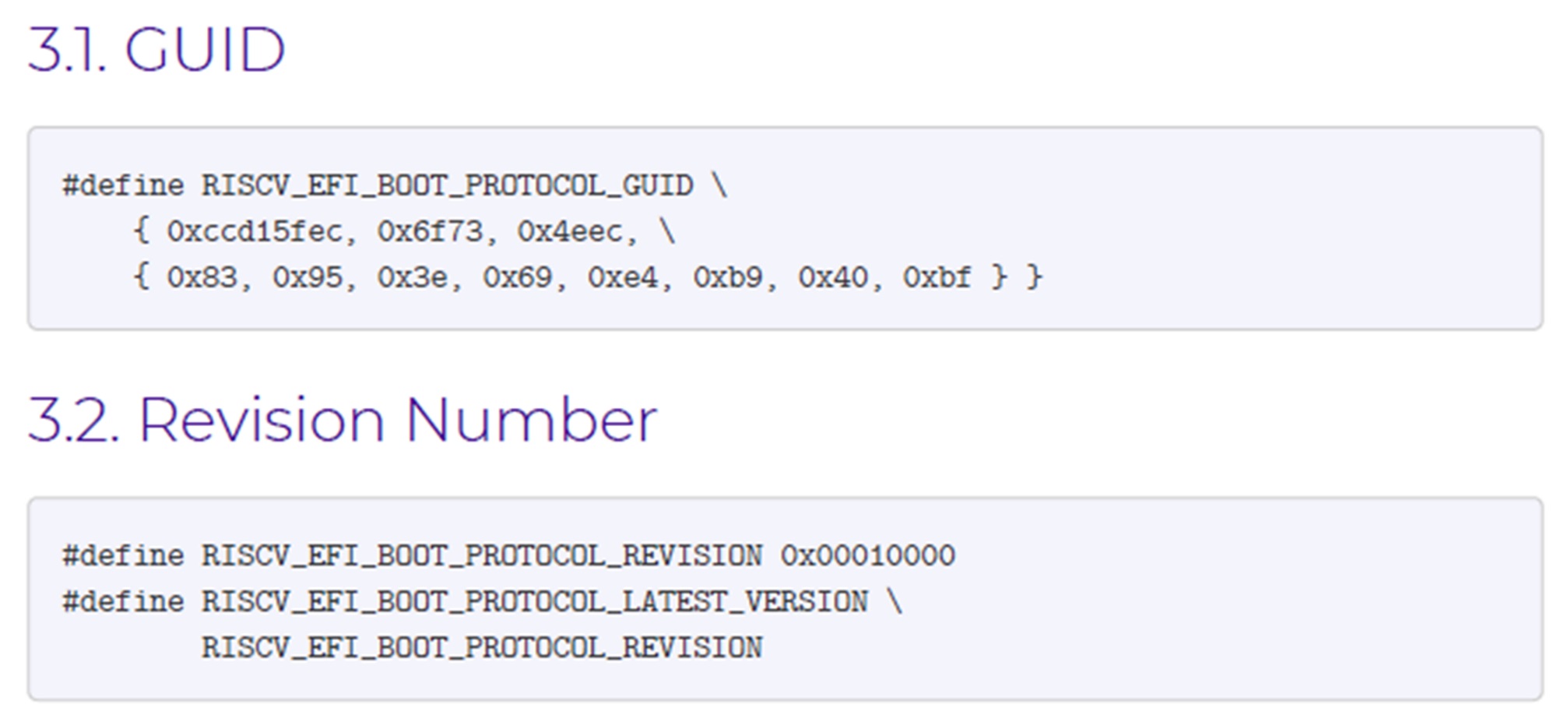

今回、UEFIの標準仕様に則った形でRISC-Vプラットフォームにおいて必要な情報がやり取りできるように、新たなインターフェース仕様として“RISCV_EFI_BOOT_PROTOCOL”が定義されました。今後RISC-VでUEFIを実装する場合、本UEFI仕様に沿った実装が必要となります。

“RISCV_EFI_BOOT_PROTOCOL”について簡単にご説明します。

以下のような、仕様自体を特定するための定義(仕様のバージョンによってユニークな値)が記述されています。

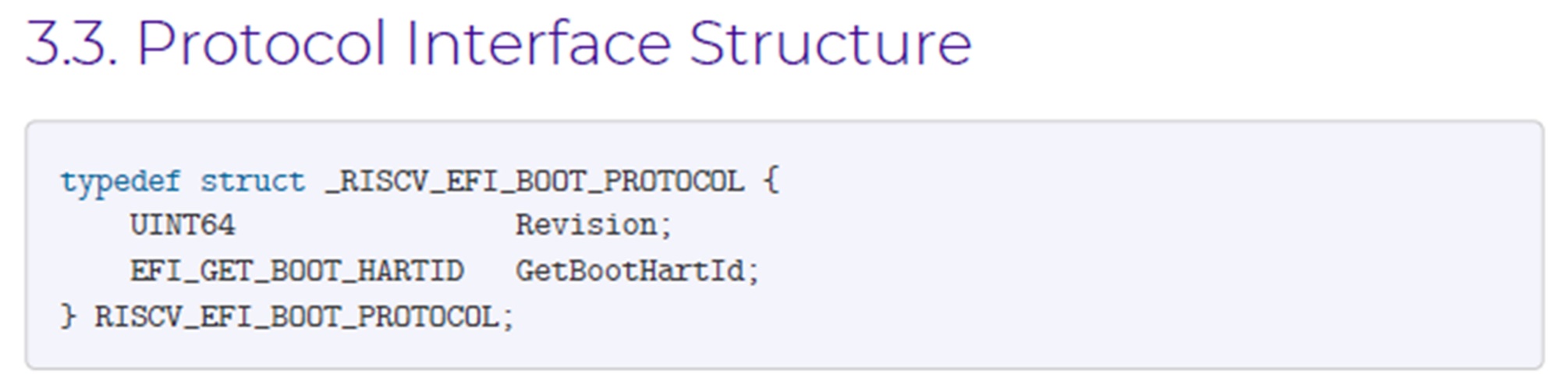

以下のようなRISC-V CPU独自の情報をやり取りするための定義(現在は ブート時CPUのhart idを取得するプロトコルのみ)が記述されています。

出典:以下のPDF中の Page 6

https://github.com/riscv-non-isa/riscv-uefi/releases/download/1.0.0/RISCV_UEFI_PROTOCOL-spec.pdf

2.4. Zmmul Multiply-Only Extension

Zmmul Multiply-Only Extension (以下、Zmmul) は、今回Ratifiedされたものの中で、唯一のISA仕様です。これまで、乗算・除算の両方がセットになったISA仕様がM Extensionとして存在していました。今回、除算を除き乗算のみのISA仕様がRatifiedされ、命令セットをZmmul として定義されました。

Zmmulで定義された命令は以下の通りです。

・MUL(Multiply)

32/64bit整数同士の乗算を行い、64/128bitの結果の下位32/64bit整数を得る

・MULH(Multiply High)

32/64bit符号付き整数同士の乗算を行い、64/128bitの結果の上位32/64bit整数を得る

・MULHU(Multiply High Unsigned)

32/64bit符号なし整数同士の乗算を行い、64/128bitの結果の上位32/64bit整数を得る

・MULHSU(Multiply High Signed-Unsigned)

32/64bit符号付き整数と符号なし整数の乗算を行い、64/128bitの結果の上位32/64bit整数を得る

・MULW (Multiply Word) ※RV64のみ有効

32bit整数同士の乗算を行い、積を32bitに切り詰め、結果を符号拡張した値を得る

出典:以下のPDF中のPage 53

https://github.com/riscv/riscv-isa-manual/releases/download/draft-20220706-f983b86/riscv-spec.pdf

3. まとめ

いかがでしたでしょうか。

RISC-V International は、RISC-V Coreを含むシステムを実現する上で、RISC-V ISAだけでなく、RISC-Vを活用するための周辺の仕様策定も重要なものとしてとらえ、ISA仕様と同様に技術検討と管理、Ratifyを実施しており、今後も仕様の拡張および追加が継続的に実施されていきます。

RISC-Vは、「シンプル」、「拡張性」、「オープン」の特徴を活かしてインダストリ、民生機器、通信、運輸、データセンターなどの領域を中心として利用が広がっていくと予想されています。

SiFiveは、RISC-V Internationalと連携し、RISC-V仕様策定に積極的に関わりを持つだけでなく、いち早くそれらの仕様に基づいて設計されたIPを継続して開発、提供しています。

本ブログについてのより詳しい内容へのご質問等ございましたら、ぜひお気軽にお問合せください。

お問い合わせはこちら

info-lsi@dts-insight.co.jp

注:

本ブログで使用しているRISC-V 仕様 に関する情報はクリエイティブ・コモンズ・ライセンス(表示4.0国際)のもとに掲載を許諾されています。

クリエイティブ・コモンズ・ライセンス(表示4.0国際)

https://creativecommons.org/licenses/by/4.0/deed.ja

■■DTSインサイトの「システムLSI設計ソリューションサービス」■■

DTSインサイトでは、システムLSI/FPGA設計の受託も行っています。

当社のノウハウを活かした、ソフトウェアの移行(マイグレーション)

サービスも提供しておりますので、お気軽にご相談ください。

システムLSI設計ソリューションサービス紹介は こちら