1.はじめに

前回まではSiFive社のRISC-V SoCが搭載されたHiFive Unleashedボードを使ったLinuxの起動方法、対応する各種Linuxディストリビューションをデモを交えてご紹介してきました。今回は、FPGAボードを使ってSiFive社のRISC-Vコアを評価する方法についてご紹介していきたいと思います。

2.FPGA開発環境 -ハードウェア編

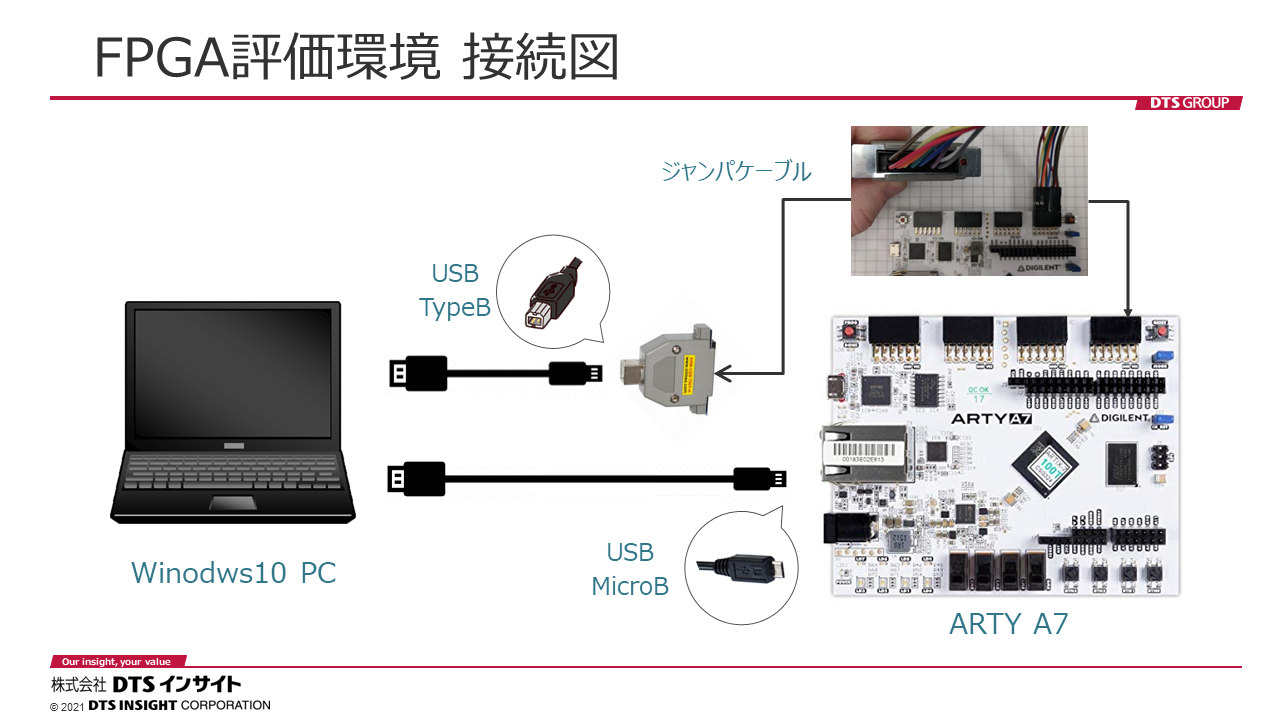

今回ご紹介するSiFive社のRISC-V コアをFPGAに実装し評価するために、以下のハードウェア環境を準備します。

a) 開発ボード : Arty A7-100T (Digilent社製 Xilinx FPGA搭載評価ボード)

b) JTAGデバッガ : OLIMEX社製ARM-USB-TINY-H

c) USBケーブル① : TypeA<=>MicroB (データ通信用)

d) USBケーブル② : TypeA<=>TypeB(データ通信用)

e) ジャンパワイヤ : OLIMEX<=>Arty PMOD 間接続用(10本)

f) ホストPC : Windows10 Pro(64bit)

これらを準備し、以下のように接続します。

これでハードウェアの準備は整いました。

3.FPGA開発環境 -ソフトウェア編

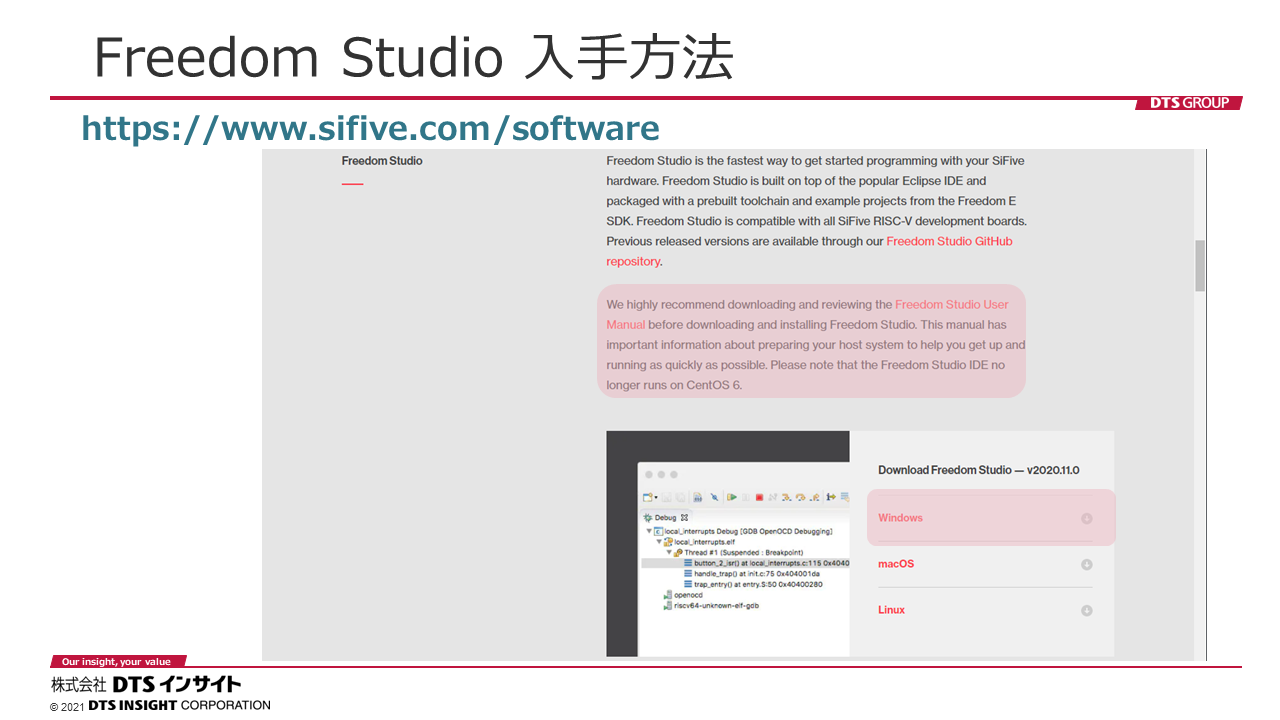

技術ブログ連載第1回でも使用しましたSiFive社が無償で提供するソフトウェア統合開発環境(IDE)であるFreedom Studioを使用します。

こちらのURLにアクセスし、Freedom Studio(※1)を入手してください。

※1 本ブログ執筆時のバージョンはv2020.11.0です。

簡単なユーザ情報の入力が必要となります。

同一ページからFreedom Studio User Manualを事前にdownloadして一読しておくことをお勧めします。

ダウンロードしたzipファイルは、”c:¥FreedomStudio”フォルダを作成し、そこに展開してください。

4.SiFive RISC-V評価用コアの入手

SiFive社のサイトから評価用のコア(Trial Dev Kit : 以下TDK)を入手します。SiFive社ではFreedom Studio同様に、簡単なユーザ登録を行うことで評価用のコアを無償で提供しています。

こちらのサイトより、右上の[Evaluate Cores]を選択し、ユーザ登録を行うことでTDKが入手できます。今回はE21コアのTDKを入手します。(※2)

※2 E2より大きいシリーズのコアの場合Arty A7-100Tには対応していないことがあります。

5.FPGA実装

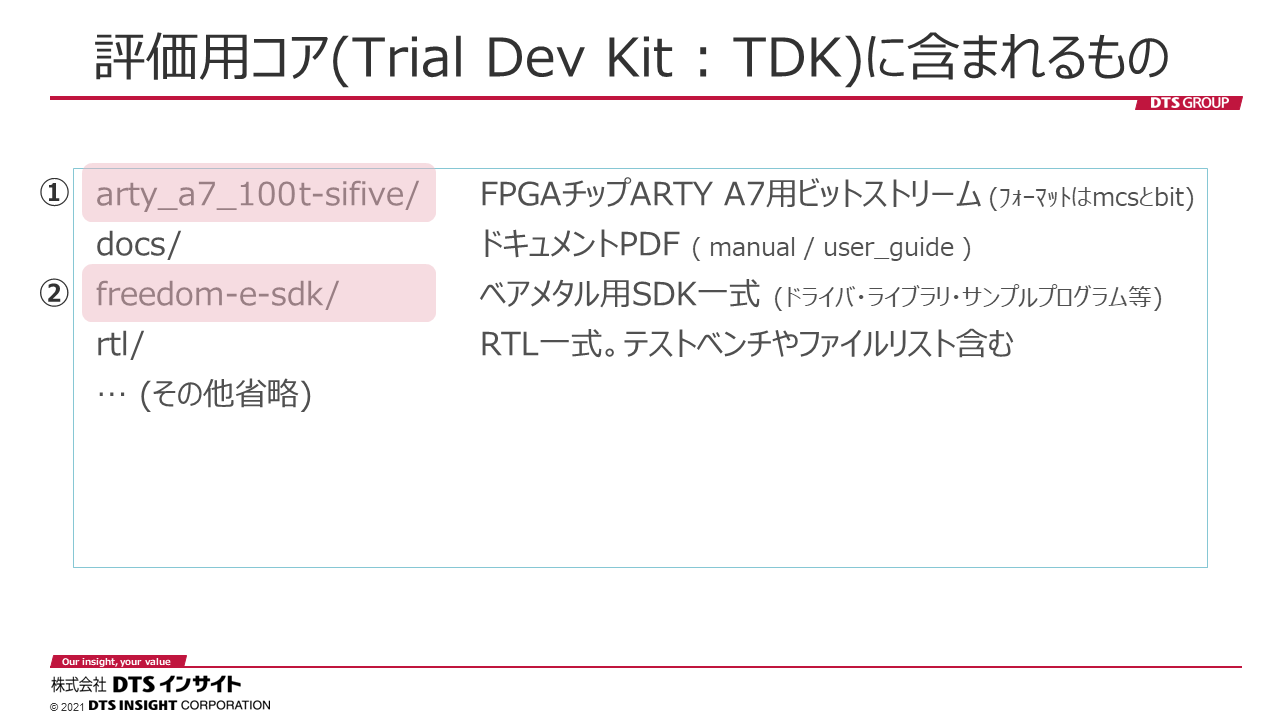

入手したTDKはtarball(圧縮したtar形式のファイル)になっているため、解凍・展開します。すると、RTL、document等の他に今回の評価で使用する、

① Arty A7-100TをターゲットとしたFPGA評価をすぐに行えるRISC-VコアのFPGA向けのビットストリーム(※3)

② ソフトウェア開発に必要なプログラム一式

※3 FPGAのコンフィグレーションに用いるデータ(FPGA image file)が含まれています。

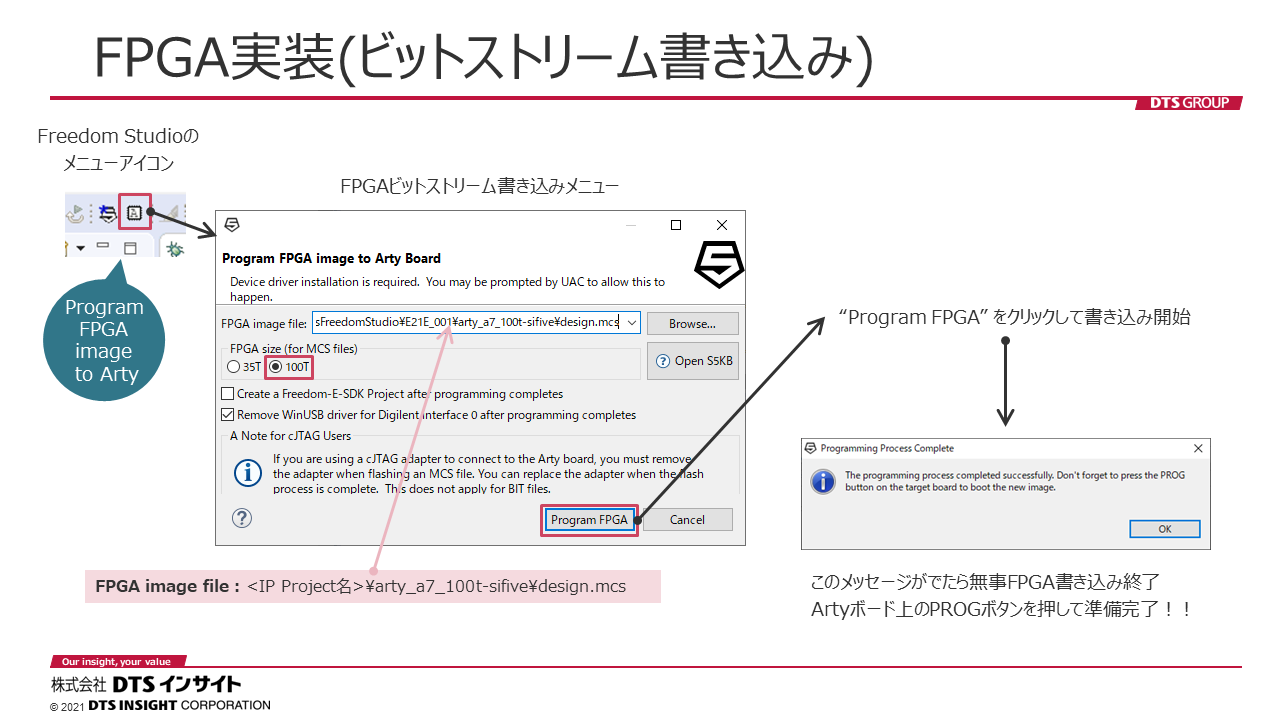

ここで、3.で入手していましたFreedom Studioを立ち上げ、手順に従いビットストリーム(design.mcs)をFPGAに書き込みます。書き込みは数分で完了し、書き込み後にFPGAボード上のPROGボタンを押下する旨のポップアップ表示されます。指示に従ってPROGボタンを押下して完了となります。

以上で今回の評価に必要なRISC-VコアのFPGA実装は完了です。

6.まとめ

今回は、SiFive社の評価用RISC-VコアをFPGAボードに実装する方法について紹介しました。次回は今回準備したFPGA評価環境において、Freedom Studioを用いたサンプルプログラムの実行から様々なデバッグ方法についてご紹介していきたいと思います。

■■DTSインサイトの「システムLSI設計ソリューションサービス」■■

DTSインサイトでは、システムLSI/FPGA設計の受託も行っています。

当社のノウハウを活かした、ソフトウェアの移行(マイグレーション)

サービスも提供しておりますので、お気軽にご相談ください。

システムLSI設計ソリューションサービス紹介は こちら