マイコン制御開発 基礎コース(オンライン)

- 日程:2026年6月18日(木)-6月19日(金)

2日間コースです

- 時間:9:00~17:00 ※終了時間は進行状況により若干変動する可能性があります。

コースの概要

本コースは、新入社員を含む組込み開発初心者の方が、組込みシステムの技術者に必要なマイコンの基礎知識について学習します。

組込みシステムで利用される技術、またその用語についての知識を得る事を目的とします。一般的な組込み開発の観点で解説していますので、Arm®以外のアーキテクチャにも応用可能です。

Day 1 マイコン入門

- CPUの(ハード的な)構成要素

- メモリ

- 例外処理

- アセンブラ命令とプログラム

- Day1のまとめ・Q&A

Day 2 マイコンの制御

- アセンブラ命令とプログラム(続き)

- ソフトウェアがペリフェラルを制御する仕組み

- 電力管理

- デバッグのコツ

- Day2のまとめ・Q&A

(※内容が一部変更になる場合がございます。その際はお申込みいただきました際にご案内申し上げます。)

受講対象者

- 組込み開発に初めて携わる新入社員・開発者様

オンライン開催にあたり

- Web会議サービス(Zoom)で開催します。

- ブラウザでのご参加は「Google Chrome」のみ対応しています。

※Google Chromeの使用ができない場合は、Zoomアプリのインストールが必要になります。

※Zoomのアウントの取得は必須ではございません。

お申し込み方法

受付終了:2026年6月9日(火)18:00まで

受講料:80,000円(受講者1名様/税抜き)

※同業者様等のお申し込みについてはお断りする場合もございます。

「マイコン制御開発 基礎コース」

お支払方法

請求書はお申し込みいただいた講座の開催が確定した後、講座の開催月にお申込書に記載されたお申込者様宛にお送りいたします。

請求書に記載される期日(請求書の発行月末締め翌月末振込み)に受講料を弊社指定銀行へお振込ください。

(振込手数料は振込者がご負担下さい。)

支払い処理について上記の方法以外をご希望の場合、 Arm®トレーニング事務局までご連絡下さい。ご相談に応じます。

お問い合わせ先

Arm®トレーニング事務局

TEL : 03-6756-9405

E-mail : arm_training@dts-insight.co.jp

コース内容

Day1 マイコン入門

1 CPUの構成要素

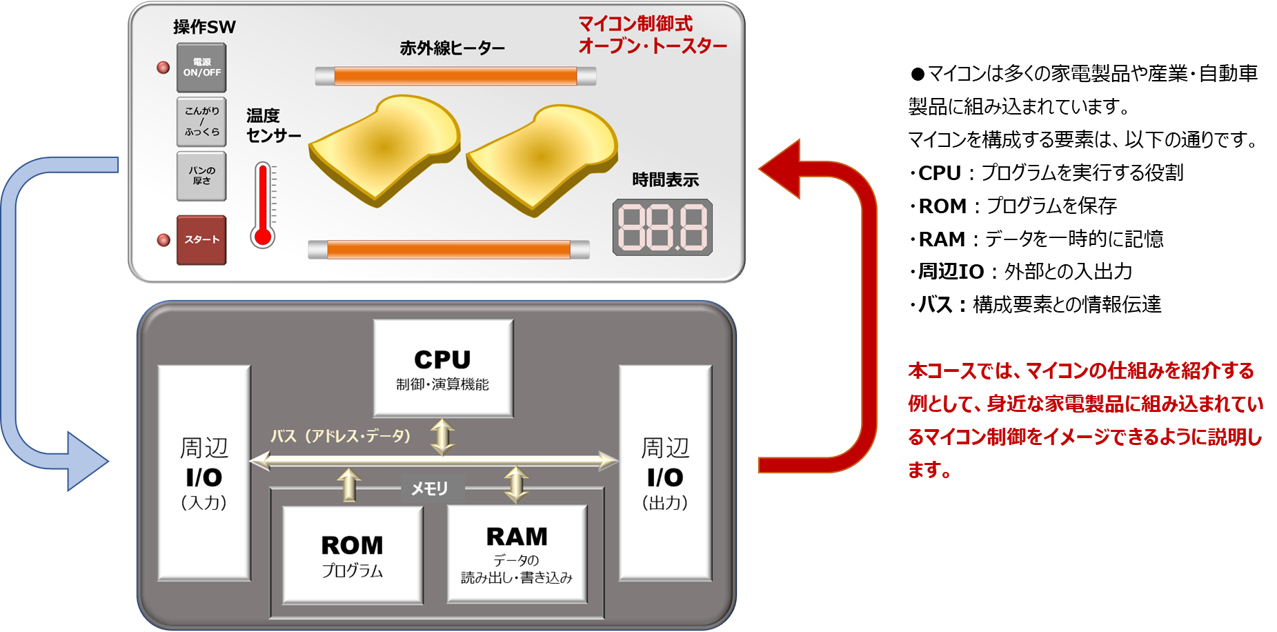

- 1.1 マイコンの構成要素

CPU(制御・演算機能)/ROM(プログラム)/RAM(データの読み出し・書き込み)/周辺IO(外部との入出力) - 1.2 マイコンの組込み応用の解説

プログラムカウンタ/命令デコーダ/キャッシュ(I/Dキャッシュ)デコーダ - 1.3 バス

バスの種類(アドレスバス・データバス・コントロールバス)/マイコン構成要素の繋がり(バス構造) ノイマン型・ハーバード型 - 1.4 CPUの基本動作

命令の取り出し・解読・実行の仕組み/PCプログラム・カウンタの機能(PCセット)/PCプログラム・カウンタの動き/CPUの基本動作/非パイプラインとパイプライン/命令レジスタへの取り込み(ferch)と命令デコード(decode)/実行処理の前準備(オペランド操作) /ALU(演算処理)と命令実行(execute) - 1.5 レジスタ

レジスタの種類/Ex.Armの場合/RISCとCISCの違い/データサイズ、状態、命令セット/特権モードとユーザーモード/Armプロセッサの動作モード/モード別レジスタ構成/汎用レジスタ/プログラムカウンタ/リンクレジスタ/サブルーチンについて/スタックポインタ/スタックについて/プログラムステータスレジスタ - 1.6 付録

数値の表現/r進数表記法/2進数と16進数表記法/整数/正数・負数/正数・負数の加算、減算/固定小数点/浮動小数点/Arm Cortex-M4 浮動小数点ユニット

2 メモリ

- 2.1 メモリ

メモリ(ROMとRAM)/SRAM/DRAM/SDRAM/リードオンリーメモリ(ROM)の種類(データフラッシュ) - 2.2 アドレスと制御信号

メモリとアドレス/アドレス・データ/CPUとメモリの接続 - 2.3 メモリマップ

メモリ空間・メモリマップ/Armのメモリマップ例/メモリマップとバス - 2.4 MPU

メモリプロテクションユニット - 2.5 付録

キャッシュの概要/キャッシュ方式/ヒットとミスヒット/ライトバッファの概要

3 例外処理

- 3.1 イントロダクション

例外とは?/概要 - 3.2 例外モデル

例外のタイプ/プロセッサモードと特権状態/特権状態/プロセッサのモードの使い方/プリエンプション(実行権の横取り)/例外優先度のモデル/例外優先度の概要/優先度による例外ハンドリングの例/例外の状態/ベクタテーブル/Arm®v7-Mのベクタテーブル

3.2.1 例外のエントリと終了の挙動

リセットの基本のエントリ動作/リセット以外の例外の基本のエントリ動作/例外エントリ時のスタッキング/ReturnAddress 値/割り込みの発生からISRが呼び出されるまで/ISRからのリターン/EXC_RETURN

3.2.2 割り込み

割り込みのメカニズム/割り込み検出/パルス割り込み– 1 パルス/パルス割り込み– 複数パルス/ レベル割り込み/外部割込み/NVIC 制御レジスタ/NVICブロック図/イネーブル レジスタ/ペンディング レジスタ/アクティブ レジスタ/プライオリティ レジスタ/割り込みがネストした場合の例/テールチェインの例

3.2.3 C/C++やアセンブラでのベクタテーブルと例外ハンドラ

Cで記述したベクタテーブルの例/アセンブラで記述したベクタテーブルの例/例外ハンドラ - 3.3 内部例外とRTOSサポート

内部割り込み/内部割り込みレジスタ/システムタイマ-SysTick - 3.4 フォールト例外

Armv7-M のフォールト例外/フォールトの処理

4 アセンブラ命令とプログラム

- 4.1 アセンブリ言語を理解する目的

- 4.2 命令セットアーキテクチャ(ISA:Instruction Set Architecture)

- 4.3 アセンブラの役割

- 4.4 擬似命令とディレクティブ

- 4.5 データ処理命令と使用可能なオペランド

データ処理命令/レジスタオペランドとイミディエイト定数オペランド/オペランド内でのシフト演算/イミディエイト定数の命令表現/LDR擬似命令(レジスタにデータを転送)/ステータスレジスタ操作命令 - 4.6 ロード/ストア命令

ロード命令(単一)/ストア命令(単一)/ロード/ストア命令とアライメント/ ロード/ストア命令(単一)アドレッシングモード - 4.7 ロード/ストア命令とスタック

ロード/ストア命令(複数)と使用可能なアドレッシングモード/ 複数レジスタのロード/ストア命令(スタック操作命令)/スタックの動き(フルディセンディング) - 4.8 条件フラグと条件つき実行

条件フラグを設定できる命令/レジスタの比較とテスト/条件付き実行/ 条件フィールドと条件フラグの対応表(参考) - 4.9 分岐命令とリンク付き分岐命令

分岐命令(条件分岐、無条件分岐)/ラベルについて/リンク付き分岐命令 - 4.10 絶対アドレスとPC相対アドレス

リロケータブルプログラム/アプリケーションプログラムのアドレス指定/絶対アドレスの指定(ロード)/PC相対アドレスの指定(ロード)

Day2 マイコンの制御

5 ソフトウェアがペリフェラルを制御する仕組み

- 5.1 周辺機能の概要

概要/ペリフェラルの例/IOレジスタ/外部端子(ピン) /外部端子(兼用端子) - 5.2 GPIO

概要/GPIOの用途・使用例/GPIOを動かすには(アクセス方法)/Ex.入力ポートの活用事例 - 5.3 タイマ

タイマ概要/用途/周期処理/タイマ割込/Ex.タイマとカウンタの関係 - 5.4 PWM

周期/タイマによるPWM波形の生成/Duty比 - 5.5 シリアル通信

通信形式(UART、SPI、I2C) /クロックとタイミング(周期、立ち下がりと立ち上がり、送受信の同期) /通信データとビット幅 - 5.6 ADコンバータ

概要/アナログ-デジタル変換/分解能/基準電圧/変換時間/Ex.ADコンバータの利用例 - 5.7 周辺回路との連携

センサーからの出力をマイコンに取り込む/マイコンからPWMを使ってモーターを制御する

6 電力管理

- 6.1 電力管理の概要

低消費電力モードの概要/活用される背景 - 6.2 低消費電力モード

低消費電力モードの機能(Arm® Cortex®-Mの場合)/低消費電力モードの例/低消費電力モードの周辺動作 - 6.3 低消費電力モードの活用事例

低消費電力モードの遷移/低消費電力モードの活用事例(SLEEP/STOP/STANDBYモードのユースケース) - 6.4 低消費電力モードの状態遷移

SLEEPモードの要件:状態監視の処理/SLEEPモードへの遷移/SLEEPモードからの解除

7 デバッグのコツ

- 7.1

はじめに(実行制御、ステート制御、実行履歴)/ブレークポイントvsウォッチポイント/ブレークポイントの種類/フォールト発生時のデバッグ方法/その他デバッグに関する注意点

※Day2は、講師によるデモ、活用事例、使用方法を紹介しながら学習を進めていきます。

(※内容が一部変更になる場合がございます。その際はお申込みいただきました際にご案内申し上げます。)